Hardware Reference

In-Depth Information

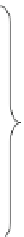

Instruction Memory

Controller

PE

PE

PE

PE

H-ch

H-ch

Data Registers

(SRAM)

PE

PE

PE

PE

Data Registers

(SRAM)

PE

PE

PE

PE

PE

PE

PE

PE

PE

PE

PE

PE

512b

512b

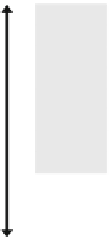

Fig. 4.24

Structure of massively parallel processor MX-2

requests to communicate with a host processor or a DMA controller. The LS cells

and the SEQM are connected to a bus interface (I/F) via an internal bus, and the

CFGM is also connected to the bus I/F, which is the interface to the system bus

SuperHyway. An I/O port is connected to the XB by an I/O port controller and

enables data transfers independent of the SuperHyway.

The FE-GA is suitable for signal processing or recognition including image and

sound data that consists of massive amount of 16-bit data and is effective for processes

with middle grain parallelism. The details of the FE-GA are described in Sect. 3.2.

4.4.3

Massively Parallel Processor MX-2

Figure

4.24

illustrates the structure of the MX-2. It is a massively parallel processor

consisting of 1,024-way-SIMD 4-bit PEs with an ALU and a booth encoder, two

SRAMs as data registers, a controller with an instruction memory, and an I/O interface

to subsystem and media buses. The number of PEs can be in multiple of 256, and each

MX-2 of the RP-X integrated 1,024 PEs. The PEs and SRAMs are connected conform-

ing horizontal channels (H-ch), and the PEs are connected by a shifter that forms

vertical channels (V-ch). The MX-2 performs efficient massively parallel arithmetic

processing. It is especially good for multiple-of-4-bit-wide data such as image data,

which are mainly 8 or 12 bits. The details of the MX-2 are described in Sect. 3.3.

4.4.4

Programmable Video Processing Core VPU5

Figure

4.25

illustrates the structure of the VPU5. It is a programmable video pro-

cessing core consisting of two codec elements for pixel-rate domain and a variable

Search WWH ::

Custom Search