Hardware Reference

In-Depth Information

1.0

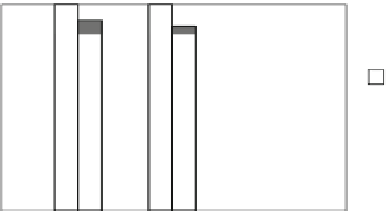

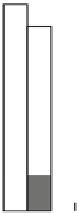

-8%

-11%

-21%

0.8

Conventional

0.6

Auto-rotating

0.4

0.2

0.0

Water

Radix

Barnes

Fig. 4.21

Processing time reduction in kernel mode

kernel mode. The reduction was 8% for Water, 11% for Radix, and 21% for Barnes,

respectively.

In addition to the improved performance, the reduction in the acknowledged

interrupts is expected to be effective for saving power. In sleep mode in particular,

the redundant interrupt handling leads to wasted power used to wake up the cores

and put them in sleep mode.

4.4

RP-X Prototype Chip

A heterogeneous multicore is one of the most promising approaches to attain high

performance with low frequency and power for consumer electronics or scientific

applications. The RP-X is the latest prototype multicore chip with eight SH-X4

cores [

18-

20

] (see Sect. 3.1.8 ), four Flexible Engine/Generic ALU Arrays (FE-GAs)

[

21,

22

], two MX-2 matrix processors [

23

], a video processing unit 5 (VPU5)

[

24,

25

], and various peripheral modules. It was fabricated using 45-nm CMOS

process. The RP-X achieved 13.7 GIPS at 648 MHz by the eight SH-X4 cores mea-

sured using the Dhrystone 2.1 benchmark and a total of 114.7 GOPS with 3.07 W.

It attained a power efficiency of 37.3 GOPS/W.

4.4.1

RP-X Speci fi cations

The RP-X specifications are summarized in Table

4.6

. It was fabricated using a

45-nm CMOS process, integrating eight SH-X4 cores, four FE-GAs, two MX-2s,

one VPU5, one SPU, and various peripheral modules as a heterogeneous multicore

SoC, which is one of the most promising approaches to attain high performance

with low frequency and power, for consumer electronics or scientific applications.

Search WWH ::

Custom Search