Hardware Reference

In-Depth Information

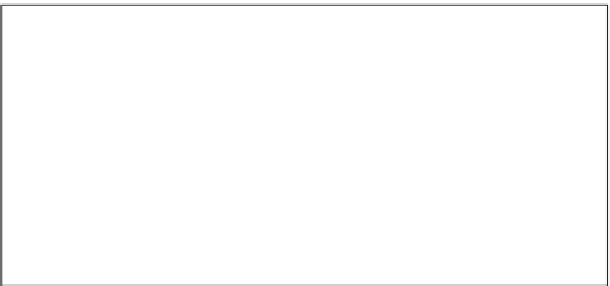

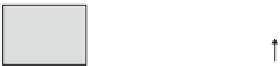

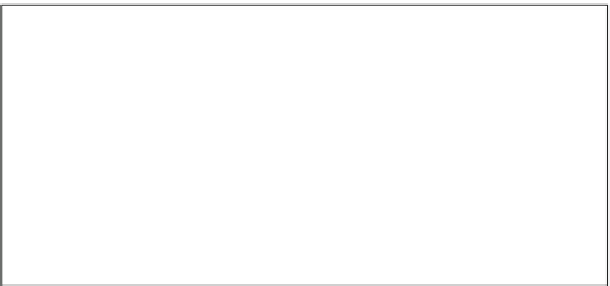

SBUS

interface

Global

DMAC

Internal bus

Stream processor memory interface

Intermediate

stream

Intermediate

stream

Initial

parameter

Firmware

Table data

On-chip

interconnect

Instruction

memory

Hardwired logic

Instruction

memory

Data

memory

Data

memory

Table

memory

Table

memory

3,220-bit

context flip-flop

CABAC accelerator

3,220-bit

context flip-flop

Memory

port

Two-way VLIW stream processor

Control

External

memory

External

memory

Initial

parameter

Initial

parameter

Intermediate

stream

Intermediate

stream

Firmware

Firmware

Table data

Table data

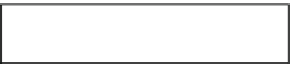

Fig. 3.86

Stream-processing unit architecture. The stream processor and CABAC accelerator are

connected to the internal bus, allowing them to access the intermediate stream buffer in an external

memory via the global DMAC

3.4.3.1

Stream Processor

Figure

3.86

shows the stream processing unit architecture, which consists of a two-

way very long instruction word (VLIW) stream processor and an H.264 context-

adaptive binary arithmetic coding (CABAC) accelerator with 3,220-bit context

flip-flops. These parts and a common SBUS interface are connected to the internal

bus so that each part can access the intermediate stream buffer in an external

SDRAM via the global DMAC. The stream processing unit can support various

video coding standards by changing the firmware, which consists of the decoder or

encoder program and the table data. The video codec loads the firmware from the

external SDRAM to the stream processing unit's internal memories before the unit

starts decoding or encoding video streams. The program in the firmware is loaded

to the stream processor's instruction memory, and the table data are loaded to the

table memory. The CABAC accelerator, which the stream processor controls,

includes context flip-flops to achieve high performance.

Figure

3.87

shows the architecture of the proposed stream processor (STX). We

employ the 32-bit 2-way VLIW, 3-stage pipelined architecture as the stream proces-

sor architecture [

77

] .

Stream encoding/decoding is divided into variable length coding, syntax analysis,

and context calculation. Variable length coding is further divided into coding/

decoding with table data (table encoding/decoding) and Golomb encoding/decoding,

which is employed in H.264. Table encoding/decoding in various video coding stan-

dards can be easily developed by changing the data in the table memory in the STX.

Search WWH ::

Custom Search