Hardware Reference

In-Depth Information

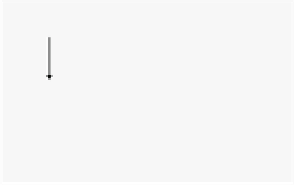

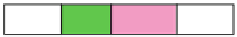

a

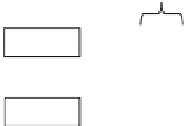

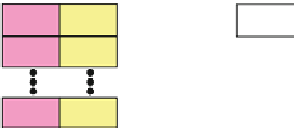

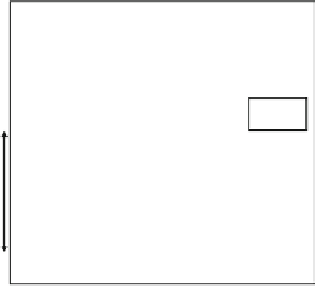

Stride

Media IPs

Media IPs

VPU

VPU

Tile

Tile

Tile

Tile

BlkV

BlkV

Virtual address (VADR)

BlkH

BlkH

Address space judgment

Address space judgment

Log2(BlkV)

Log2(Stride)

VADR

23:16

23:16

VB5

VB5

HB6

HB6

TB5

TB5

PMB

16 entries

16MB page

PMB

16 entries

16MB page

Tile-linear

address

translator

Tile-linear

address

translator

PADR

23:16

23:16

HB6

HB6

VB5

VB5

TB5

TB5

Media interconnect

Media interconnect

On-chip interconnect

On-chip interconnect

Log2(BlkH)

Physical address (PADR)

Off-chip memory

Off-chip memory

Tile-linear address transition circuits.

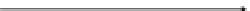

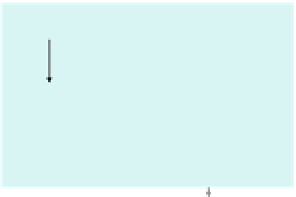

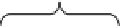

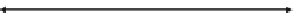

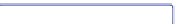

b

VADR (Tile-based addressing)

PADR (Linear addressing)

32Byte

Stride=2048Byte

Stride=2048Byte

0

1

0

1

32

33

32

33

64

65

64

65

2016

0

1

31

32

63

64

65

95

96

127

31

31

63

63

95

95

2047

2016

2047

2048

2049

2048

2049

2048

2048

2049

2049

2079

2079

page = 1024Byte

Image plane

2079

2079

Memory allocation in virtual and physical address space.

Fig. 3.85

Tile-linear address translation (TLAT)

motion estimators/motion compensators (FME), two transformers (TRF), and two

in-loop deblocking filters (DEB), which are depicted in Fig.

3.76

, are implemented

as low-power media processors called programmable image processing elements

(PIPE).

Search WWH ::

Custom Search