Hardware Reference

In-Depth Information

Instruction

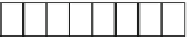

RAM

MX Processor Controller (MPC)

Control Signals

PE

PE

PE

PE

Data Registers

(SRAM)

Data Registers

(SRAM)

V-ch

H-ch

PE

PE

256b

256b

MX Processor Array (MPA)

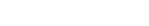

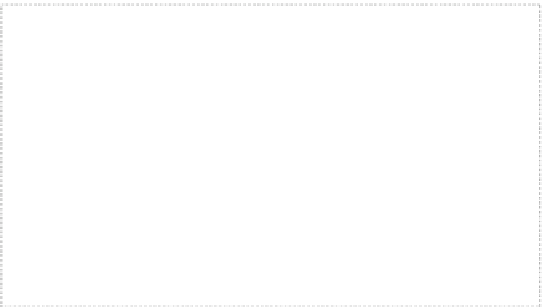

Fig. 3.61

MX-1 architecture

3.3.1

MX-1

3.3.1.1

Architecture Overview

Applications like image processing and recognition which are employed in the por-

table devices demand the processing ability of up to several tens of GOPS, which is

far beyond the capabilities of conventional CPUs or DSPs. In these areas which

require high performance, hard-wired logic LSIs are commonly used to realize both

high-performance and low-power dissipations. However, hard-wired solutions have

problems in cost efficiency because algorisms for media processing are being

improved at short intervals. Therefore, powerful and also programmable devices are

desired to be employed in these multimedia applications. Considering these back-

grounds, our motivation is to improve energy efficiencies and flexibilities of SIMD

architectures while realizing a high performance which is enough for the multime-

dia applications.

Figure

3.61

shows the overview of the MX-1 architecture [

55,

56

] . MX-1 is the

first version of the MX core. MX-1 consists of matrix processor array (MPA), matrix

processor controller (MPC) which is a dedicated controller with an instruction

memory, and the I/O interface for data I/O. The main components of MPA are two

planes of data register array matrices, fine-grained (2-bit) 2,048 processing elements

(PE). The data register array matrices are composed of single-port SRAM cells to

enhance the area efficiency. PE adopts a 2-bit-grained structure, which includes two

full adders and some logic circuits, to minimize the size of each PE.

As shown in Fig.

3.61

, there are two-directional channels for data processing.

One is the Horizontal channel (H-ch) which connects the data register array matri-

ces and PEs. The other is the Vertical channel (V-ch) which realizes the flexible data

Search WWH ::

Custom Search