Hardware Reference

In-Depth Information

Fig. 7.2

The structure of a

sequential network

cs

o

ns

i

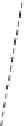

Fig. 7.3

An example

of sequential network

o

cs

2

cs

1

ns

2

ns

1

i

of such networks are the primary inputs (

i

), the primary outputs (

o

), and the latches

having the current state (

cs

) and next state (

ns

) variables. We assume that the latch

next-state functions,

T

k

.i; cs/

, and the primary-output functions,

O

j

.i; cs/

, can be

computed and stored as BDDs in terms of the primary inputs and the current state

variables.

The automata for

F

and

S

are derived from the multi-level networks representing

them, simply by taking the set of inputs of these automata as the union of the sets of

inputs and outputs of the corresponding network. All reachable states of a network

are the accepting states of the corresponding automaton, since

F

and

S

are FSMs

and hence are prefix-closed. A “don't-care” (

DC

) state can be added to make an

automaton complete. This is done by making all automaton input combinations, for

which the behavior of a state is not defined, transition to

DC

, which becomes the

only non-accepting state. The requirement of prefix-closed dictates that

DC

has a

universal self-loop.

Example 7.1.

Figure

7.3

shows a sequential circuit, while Fig.

7.4

a,b show respec-

tively the corresponding FSM and automaton. The circuit has input

i

, output

o

,

Search WWH ::

Custom Search