Information Technology Reference

In-Depth Information

separately added and removed from running domains using DR, provided they are

not already assigned to other domains.

Domains run applications in strict isolation from applications running in other

domains. Isolation and security between domains are maintained by an important

ASIC called the system controller (SC), which ensures that one domain cannot

access data packets from another domain.

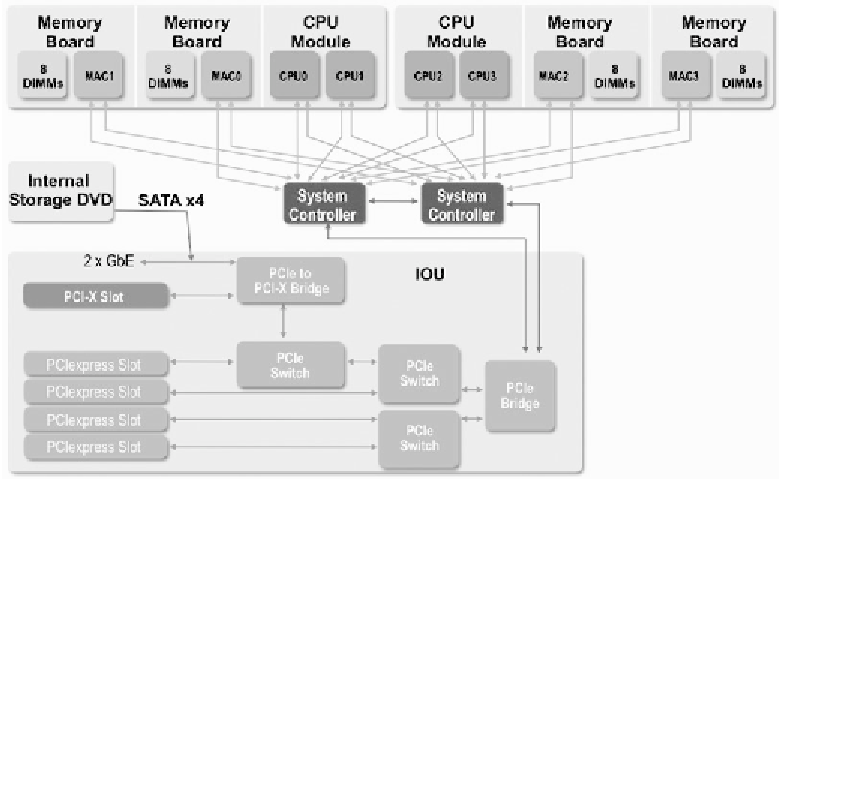

The M4000/M5000 block diagram in Figure 2.1 shows how memory accesses

and I/O transactions pass through the SC. Because the memory access controller

(MAC) is not in the CPU but rather is found in a separate ASIC, a CPU's accesses

to memory go through the SC. This arrangement allows it to enforce all domain

data pathways for complete domain isolation. The SC is also important in ensur-

ing balanced memory access performance. The physical pages of memory on the

board are spread evenly across the SC chips for balanced memory throughput—

another reason why the SC chip is one of the most critical ASICs in the system.

Figure 2.1

Block Diagram of M4000/M5000

The I/O assembly is called the I/O unit (IOU). Also note that there are two PCIe

switches per IOU in the M4000/M5000. As a consequence, each IOU can support

two domains, but each domain has access to different PCIe slots and storage.

(This approach will be explained later when describing the Quad-XSB mode set-

ting for the system board.) The PCIe to PCI-X bridge in the IOU is used to access

the two built-in gigabit Ethernet ports and the internal boot drives. If the entire

Search WWH ::

Custom Search