Hardware Reference

In-Depth Information

Stage 3 locates and fetches the operands, either from registers or from memory.

Stage 4 actually does the work of carrying out the instruction, typically by running

the operands through the data path of Fig. 2-2. Finally, stage 5 writes the result

back to the proper register.

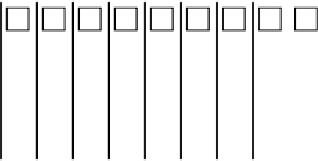

S1

S2

S3

S4

S5

Instruction

fetch

unit

Instruction

decode

unit

Operand

fetch

unit

Instruction

execution

unit

Write

back

unit

(a)

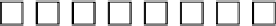

S1:

S2:

S3:

S4:

S5:

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

…

1

2

3

4

5

6

7

1

2

3

4

5

6

1

2

3

4

5

123456789

Time

(b)

Figure 2-4.

(a) A five-stage pipeline. (b) The state of each stage as a function of

time. Nine clock cycles are illustrated.

In Fig. 2-4(b) we see how the pipeline operates as a function of time. During

clock cycle 1, stage S1 is working on instruction 1, fetching it from memory. Dur-

ing cycle 2, stage S2 decodes instruction 1, while stage S1 fetches instruction 2.

During cycle 3, stage S3 fetches the operands for instruction 1, stage S2 decodes

instruction 2, and stage S1 fetches the third instruction. During cycle 4, stage S4

executes instruction 1, S3 fetches the operands for instruction 2, S2 decodes in-

struction 3, and S1 fetches instruction 4. Finally, in cycle 5, S5 writes the result of

instruction 1 back, while the other stages work on the following instructions.

Let us consider an analogy to clarify the concept of pipelining. Imagine a cake

factory in which the baking of the cakes and the packaging of the cakes for ship-

ment are separated. Suppose that the shipping department has a long conveyor belt

with five workers (processing units) lined up along it. Every 10 sec (the clock

cycle), worker 1 places an empty cake box on the belt. The box is carried down to

worker 2, who places a cake in it. A little later, the box arrives at worker 3's sta-

tion, where it is closed and sealed. Then it continues to worker 4, who puts a label

on the box. Finally, worker 5 removes the box from the belt and puts it in a large

container for later shipment to a supermarket. Basically, this is the way computer

pipelining works, too: each instruction (cake) goes through several processing

steps before emerging completed at the far end.