Hardware Reference

In-Depth Information

While programmers just think about 0s and 1s, engineers have to worry about

things like how the customer will get the product through the door and into the

building.

System control board

9

CPU-memory

boards

CPU

Memory

CPU

Memory

Memory

CPU

CPU

Memory

CPU

Memory

CPU

Memory

CPU

Memory

CPU

Memory

PCI cont.

PCI cont.

9 I/O

boards

PCI cont.

PCI cont.

PCI slot

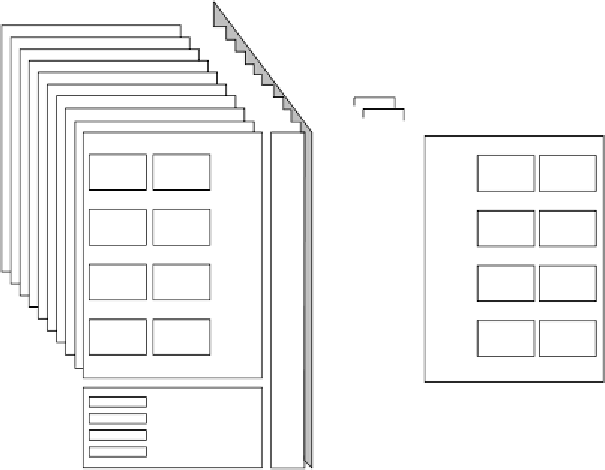

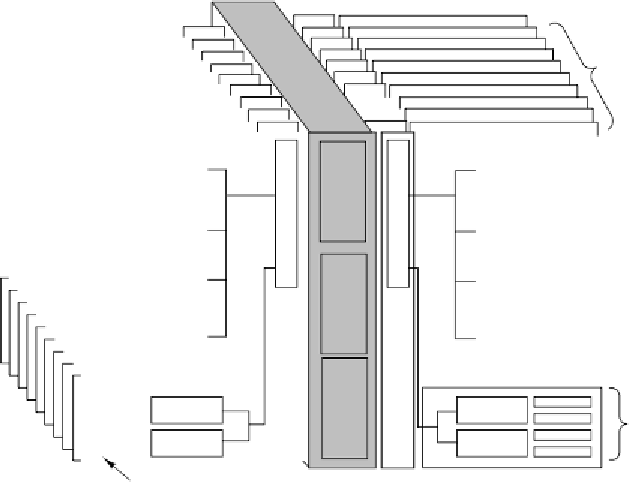

Figure 8-34.

The Sun Microsystems E25K multiprocessor.

The centerplane is composed of a set of three 18

18 crossbar switches for

connecting the 18 boardsets. One crossbar is for the address lines, one is for re-

sponses, and one is for data transfer. In addition to the 18 expander boards, the cen-

terplane also has a system control boardset plugged into it. This boardset has a sin-

gle CPU but also interfaces to the CD-ROM, tape, serial lines, and other peripheral

devices needed for booting, maintaining, and controlling the system.

The heart of any multiprocessor is the memory subsystem. How does one con-

nect 144 CPUs to the distributed memory? The straightforward ways—a big shar-

ed snooping bus or a 144

×

72 crossbar switch—do not work well. The former

fails due to the bus being a bottleneck and the latter fails because the switch is too

difficult and expensive to build. Thus large multiprocessors such as the E25K are

forced to use a more complex memory subsystem.

At the boardset level, snooping logic is used so all local CPUs can check all

memory requests coming from the boardset to references to blocks they currently

have cached. Thus when a CPU needs a word from memory, it first converts the

virtual address to a physical address and checks its cache. (Physical addresses are

43 bits, but packaging restrictions limit memory to 576 GB.) If the cache block it

×