Hardware Reference

In-Depth Information

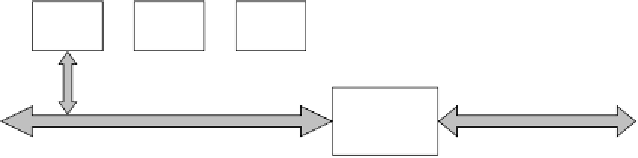

Fast

I/O

Device

register

bus

Control

CPU

Other

CPU

I/O

device

I/O

device

Arbiter

Device

Bus

bridge

Peripheral bus

Processor bus

Memory

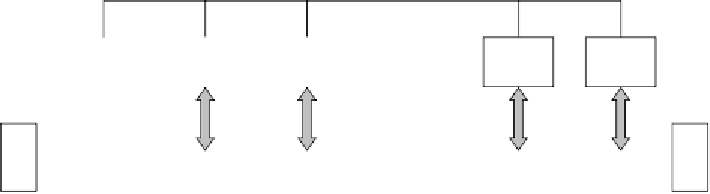

Figure 8-13.

An example of the IBM CoreConnect architecture.

The pipelining features allow cores to request the bus while a transfer is going on,

and allow different cores to use different lines at the same time, similar to the PCI

bus. The processor bus is optimized for short block transfers. It is intended to

connect fast cores, such as CPUs, MPEG-2 decoders, high-speed networks, and

similar items.

Stretching the processor bus over the entire chip would reduce its performance,

so a second bus is present for low-speed I/O devices, such as UARTs, timers, USB

controllers, serial I/O devices, and so forth. This

peripheral bus

has been de-

signed to simplify interfacing 8-, 16-, and 32-bit peripherals to it using no more

than a few hundred gates. It, too, is a synchronous bus, with a maximum through-

put of 300 Mbps. The two buses are connected by a bridge, not unlike the bridges

that were used to connect the PCI and ISA buses in PCs until the ISA bus was

phased out a number of years ago.

The third bus is the

device register bus

, a very low-speed, asynchronous,

handshaking bus used to allow the processors to access the device registers of all

the peripherals in order to control the corresponding devices.

It is intended for

infrequent transfers of only a few bytes at a time.

By providing a standard on-chip bus, interface, and framework, IBM hopes to

create a miniature version of the PCI world, in which many manufacturers produce

processors and controllers that plug together easily. One difference, however, is

that in the PCI world the manufacturers produce and sell actual boards that PC

vendors and end users buy. In the CoreConnect world, third parties design cores

but do not manufacture them. Instead, they license them as intellectual property to

consumer electronics and other companies, which then design custom heteroge-

neous multiprocessor chips based on their own and licensed third-party cores.

Since manufacturing such large and complex chips requires a massive investment