Hardware Reference

In-Depth Information

The remaining modes are usable only by load and store instructions. The third

mode is direct addressing, where the operand is in memory at an address contained

in the instruction itself. For 16-bit instructions, the direct address is limited to 7

bits (thus only addresses 0 to 127 can be loaded). The AVR architecture also de-

fines a 32-bit instruction as well that accommodates a 16-bit direct address, which

supports up to 64 KB of memory.

The fourth mode is register indirect, in which a register contains a pointer to

the operand. Since the normal registers are 8 bits wide, the load and store instruc-

tions use register pairs to express a 16-bit address. A register pair can address up to

64 KB of memory. The architecture supports the use of three register pairs:

X

,

Y

,

and

Z

, which are formed from the register pairs

R26

/

R27

,

R28

/

R29

, and

R30

/

R31

, re-

spectively. To load an address into the

X

register for example, the program would

have to load an 8-bit value into the

R26

and

R27

registers, using two load instruc-

tions.

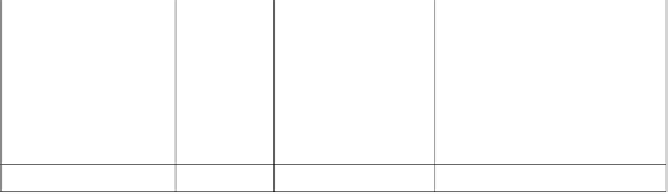

We have now studied quite a few addressing modes. The ones used by the

Core i7, OMAP4430, and ATmega168 are summarized in Fig. 5-28. As we have

pointed out, however, not every mode can be used in every instruction.

Addressing mode

Core i7

OMAP4430 ARM

ATmega168 AVR

Immediate

×

×

×

Direct

×

×

Register

×

×

×

Register indirect

×

×

×

Indexed

×

×

Based-indexed

×

Figure 5-28.

A comparison of addressing modes.

In practice, not many addressing modes are needed for an effective ISA. Since

most code written at this level these days will be generated by compilers (except

possibly for the ATmega168), the most important aspect of an architecture's ad-

dressing modes is that the choices be few and clear, with costs (in terms of execu-

tion time and code size) that are readily computable. What that generally means is

that a machine should take an extreme position: either it should offer every pos-

sible choice, or it should offer only one. Anything in between means that the com-

piler is faced with choices that it may not have the knowledge or sophistication to

make.

Thus the cleanest architectures generally have only a very small number of ad-

dressing modes, with strict limits on their use. In practice, having immediate,

direct, register, and indexed mode is generally enough for almost all applications.