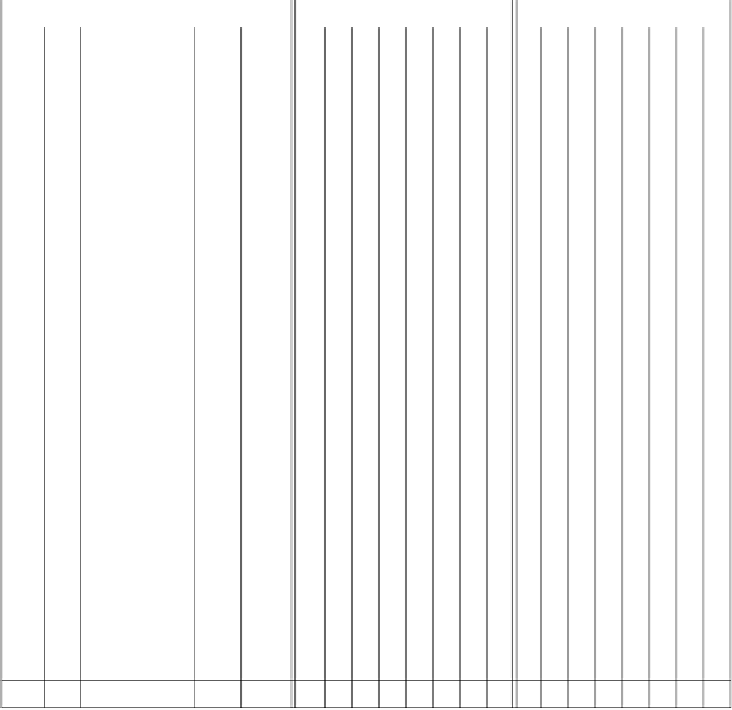

Hardware Reference

In-Depth Information

Registers being read

Registers being written

Cy

#

Decoded

Iss Ret 0123456701234567

1

1

R3=R0

*

R1

1

1 1

1

2

R4=R0+R2

2

2 1 1

1 1

2

3

R5=R0+R1

3

3 2 1

1 1 1

4

R6=R1+R4

-

3 2 1

1 1 1

3

321

111

4

1 211

11

211

1

3

5

4

1

1

1

5

R7=R1

*

R2

5

2 1

1

1 1

6

6

R1=R0

−

R2

-

2 1

1

1 1

7

4

1 1

1

8

5

9

6

1

1

1

7

R3=R3

*

R1

-

1

1

1

10

1

1

1

11

6

12

7

1

1

1

8

R1=R4+R4

-

1

1

1

13

1

1

1

14

1

1

1

15

7

16

8

2

1

17

2

1

18

8

Figure 4-43.

A superscalar CPU with in-order issue and in-order completion.

In real machines, the scoreboard also keeps track of functional unit usage, to

avoid issuing an instruction for which no functional unit is available. For simpli-

city, we will assume there is always a suitable functional unit available, so we will

not show the functional units on the scoreboard.

The first line of Fig. 4-43 shows I1 (instruction 1), which multiplies

R0

by

R1

and puts the result in

R3

. Since none of these registers are in use yet, the instruc-

tion is issued and the scoreboard is updated to reflect that

R0

and

R1

are being read

and

R3

is being written. No subsequent instruction can write into any of these or

can read

R3

until I1 has been retired. Since this instruction is a multiplication, it

will be finished at the end of cycle 4. The scoreboard values shown on each line

reflect their state after the instruction on that line has been issued. Blanks are 0s.