Hardware Reference

In-Depth Information

Final

Goto

Micro-op

ROM

index

IJVM

length

Queueing unit

3

1

2

From

memory

Micro-operation ROM

IADD

ISUB

ILOAD

IFLT

Instruction

fetch unit

Decoding unit

Queue

of pending

micro-ops

To/from

memory

Drives stage 4

M

AB

MIR1

ALU

C

4

Registers

7

MIR2

ALU

C MAB

Drives stage 5

C

MAB

Drives stage 6

ALU

MIR3

6

MIR4

ALU

C

M

AB

Drives stage 7

C

A

B

ALU

5

Shifter

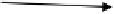

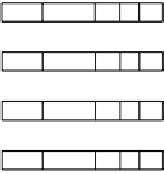

Figure 4-35.

The main components of the Mic-4.

The micro-operations are similar to the microinstructions of Fig. 4-5 except

that the

NEXT ADDRESS

and

JAM

fields are absent and a new encoded field is need-

ed to specify the A bus input. Two new bits are also provided: Final and Goto.

The Final bit is set on the last micro-operation of each IJVM micro-operation se-

quence to mark it. The Goto bit is set to mark micro-operations that are condi-

tional microbranches. They have a different format from the normal micro-opera-

tions, consisting of the

JAM

bits and an index into the micro-operation ROM.

Microinstructions that previously did something with the data path and also per-

formed a conditional microbranch (e.g.,

iflt4

) now have to be split up into two

micro-operations.

The queueing unit works as follows. It receives a micro-operation ROM index

from the decoding unit. It then looks up the micro-operation and copies it into an

internal queue. Then it copies the following micro-operation into the queue as

well, and the one after it too. It keeps going until it hits one with the Final bit on.

It copies that one, too, and stops. Assuming that it has not hit a micro-operation