Hardware Reference

In-Depth Information

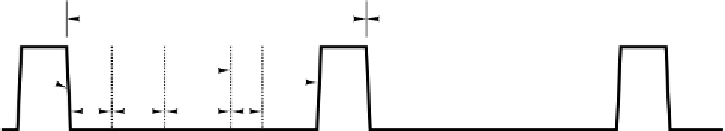

Registers loaded from

C bus and memory on

rising edge of clock

Shifter

output

stable

Cycle 1

starts

here

Clock cycle 1

Clock cycle 2

New MPC used to

load MIR with next

microinstruction here

Δ

w

Δ

x

Δ

y

Δ

z

MPC

available

here

Set up

signals

to drive

data path

ALU

and

shifter

Drive H

and

Bbus

Propagation

from shifter

to registers

Figure 4-3.

Timing diagram of one data path cycle.

B bus does not cause the C bus to change until a finite time later (due to the finite

delays of each step). Consequently, even if a store changes one of the input regis-

ters, the value will be safely tucked away in the register long before the

(now-incorrect) value being put on the B bus (or

H

) can reach the ALU.

Making this design work requires rigid timing, a long clock cycle, a known

minimum propagation time through the ALU, and a fast load of the registers from

the C bus. However, with careful engineering, the data path can be designed so

that it functions correctly all the time. Actual machines work this way.

A somewhat different way to look at the data path cycle is to think of it as bro-

ken up into implicit subcycles. The start of subcycle 1 is triggered by the falling

edge of the clock. The activities that go on during the subcycles are shown below

along with the subcycle lengths (in parentheses).

1. The control signals are set up (

w

).

2. The registers are loaded onto the B bus (

Δ

Δ

x

).

3. The ALU and shifter operate (

y

).

4. The results propagate along the C bus back to the registers (

Δ

Δ

z

).

The time interval after

z

provides some tolerance since the times are not exact.

At the rising edge of the next clock cycle, the results are stored in the registers.

Δ