Hardware Reference

In-Depth Information

protocols make for a modular and flexible design, and have been widely used in

the world of network software for decades. What is new here is building them into

the ''bus'' hardware.

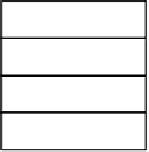

The PCI Express protocol stack is shown in Fig. 3-57(a). It is discussed below.

Software layer

Transaction layer

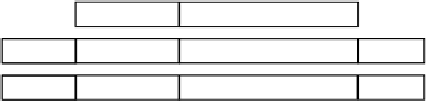

Header

Payload

Seq #

Header

Payload

CRC

Link layer

Frame

Seq #

Header

Payload

CRC

Frame

Physical layer

(a)

(b)

Figure 3-57.

(a) The PCI Express protocol stack. (b) The format of a packet.

Let us examine the layers from the bottom up. The lowest is the

physical

layer

. It deals with moving bits from a sender to a receiver over a point-to-point

connection. Each point-to-point connection consists of one or more pairs of sim-

plex (i.e., unidirectional) links. In the simplest case, there is one pair in each direc-

tion, but having 2, 4, 8, 16, or 32 pairs is also allowed. Each link is called a

lane

.

The number of lanes in each direction must be the same. First-generation products

must support a data rate each way of at least 2.5 Gbps, but the speed is expected to

migrate to 10 Gbps each way fairly soon.

Unlike the ISA/EISA/PCI buses, PCI Express does not have a master clock.

Devices are free to start transmitting as soon as they have data to send. This free-

dom makes the system faster but also leads to a problem. Suppose that a 1 bit is

encoded as +3 volts and a 0 bit as 0 volts. If the first few bytes are all 0s, how does

the receiver know data are being transmitted? After all, a run of 0 bits looks the

same as an idle link. The problem is solved using what is called

8b/10b encoding

.

In this scheme, 10 bits are used to encode 1 byte of actual data in a 10-bit symbol.

Of the 1024 possible 10-bit symbols, the legal ones have been chosen to have

enough clock transitions to keep the sender and receiver synchronized on the bit

boundaries even without a master clock. A consequence of 8b/10b encoding is that

a link with a gross capacity of 2.5 Gbps can carry only 2 Gbps of (net) user data.

Whereas the physical layer deals with bit transmission, the

link layer

deals

with packet transmission. It takes the header and payload given to it by the

transaction layer and adds to them a sequence number and an error-correcting code

called a

CRC

(

Cyclic Redundancy Check

). The CRC is generated by running a

certain algorithm on the header and payload data. When a packet is received, the

receiver performs the same computation on the header and data and compares the

result with the CRC attached to the packet. If they agree, it sends back a short

acknowledgment packet

affirming its correct arrival. If they disagree, the re-

ceiver asks for a retransmission. In this manner, data integrity is greatly improved