Hardware Reference

In-Depth Information

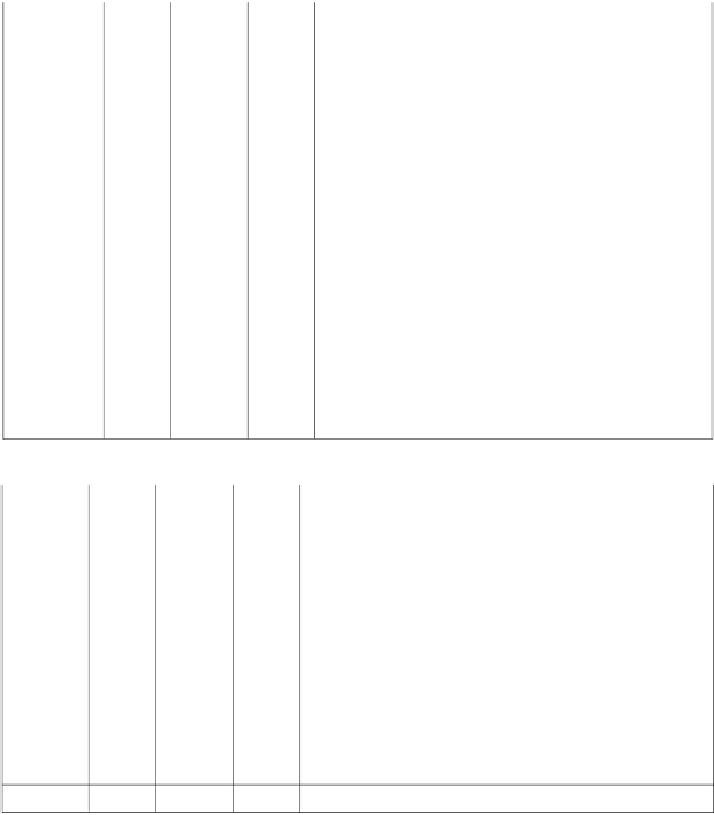

Signal

Lines Master Slave

Description

CLK

1

Clock (33 or 66 MHz)

AD

32

×

×

Multiplexed address and data lines

PAR

1

×

Address or data parity bit

C/BE

4

×

Bus command/bit map for bytes enabled

FRAME#

1

×

Indicates that AD and C/BE are asserted

IRDY#

1

×

Read: master will accept; write: data present

IDSEL

1

×

Select configuration space instead of memory

DEVSEL#

1

×

Slave has decoded its address and is listening

TRDY#

1

×

Read: data present; write: slave will accept

STOP#

1

×

Slave wants to stop transaction immediately

PERR#

1

Data parity error detected by receiver

SERR#

1

Address parity error or system error detected

REQ#

1

Bus arbitration: request for bus ownership

GNT#

1

Bus arbitration: grant of bus ownership

RST#

1

Reset the system and all devices

(a)

Signal

Lines Master Slave

Description

REQ64#

1

×

Request to run a 64-bit transaction

ACK64#

1

×

Permission is granted for a 64-bit transaction

AD

32

×

Additional 32 bits of address or data

PAR64

1

×

Parity for the extra 32 address/data bits

C/BE#

4

×

Additional 4 bits for byte enables

LOCK

1

×

Lock the bus to allow multiple transactions

SBO#

1

Hit on a remote cache (for a multiprocessor)

SDONE

1

Snooping done (for a multiprocessor)

INTx

4

Request an interrupt

JTAG

5

IEEE 1149.1 JTAG test signals

M66EN

1

Wired to power or ground (66 MHz or 33 MHz)

(b)

Figure 3-54.

(a) Mandatory PCI bus signals. (b) Optional PCI bus signals.

The next three signals are for error reporting. The first of these is

STOP#

,

which the slave asserts if something disastrous happens and it wants to abort the

current transaction. The next one,

PERR#

, is used to report a data parity error on

the previous cycle. For a read, it is asserted by the master; for a write it is asserted

by the slave. It is up to the receiver to take the appropriate action. Finally,

SERR#

is for reporting address errors and system errors.