Hardware Reference

In-Depth Information

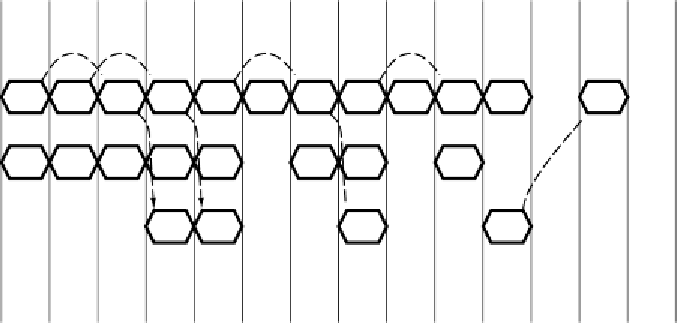

banks, even if they are contained in the same chip. A typical DDR3 DRAM chip

will have as many as 8 banks of DRAM. However, the DDR3 interface specif-

ication allows only up to four concurrent accesses on a single DDR3 channel. The

timing diagram in Fig. 3-46 illustrates the Core i7 making 4 memory accesses to

three distinct DRAM banks. The accesses are fully overlapped, such that the

DRAM reads occur in parallel within the DRAM chip. The figure shows which

commands lead to later operations through the use of arrows in the timing diagram.

Bus Cycle

0

1

2

3

4

5

6

7

8

9

10

11

12

13

CK

CMD

ACT

bank 0

ACT

bank 1

READ

bank 0

READ

bank 1

ACT

bank 2

PCHRG

bank 0

READ

bank 2

ACT

bank 0

PCHRG

bank 1

READ

bank 0

PCHRG

bank 2

PCHRG

bank 0

row

bank 0

row

bank 1

col

bank 0

col

bank 1

row

bank 2

col

bank 2

row

bank 0

col

bank 0

ADDR

data

bank 0

data

bank 1

data

bank 2

data

bank 0

DATA

Figure 3-46.

Pipelining memory requests on the Core i7's DDR3 interface.

As shown in Fig. 3-46, the DDR3 memory interface has four primary signal

paths: bus clock (CK), bus command (CMD), address (ADDR), and data (DATA).

The bus clock signal CK orchestrates all bus activity. The bus command CMD in-

dicates what activity is requested of the connect DRAM. The ACTIVATE com-

mand specifies the address of the DRAM row to open via the ADDR signal. When

a READ is executed, the DRAM column address is given via the ADDR signals,

and the DRAM produces the read value a fixed time later on the DATA signals.

Finally, the PRECHARGE command indicates the bank to precharge via the

ADDR signals. For the purpose of the example, the ACTIVATE command must

precede the first READ to the same bank by two DDR3 bus cycles, and data are

produced one bus cycle after the READ command. Additionally, the

PRECHARGE operation must occur at least two bus cycles after the last READ

operation to the same DRAM bank.

The parallelism in the memory requests can be seen in the overlapping of the

READ requests to the different DRAM banks. The first two READ accesses to

banks 0 and 1 are completely overlapped, producing results in bus cycles 3 and 4,

respectively. The access to bank 2 partially overlaps with the first access of bank 1,

and finally the second read of bank 0 partially overlaps with the access to bank 2.