Hardware Reference

In-Depth Information

putting the memory on a separate bus from the I/O devices so they do not have to

compete for access to the bus.

Decentralized bus arbitration is also possible. For example, a computer could

have 16 prioritized bus request lines. When a device wants to use the bus, it asserts

its request line. All devices monitor all the request lines, so at the end of each bus

cycle, each device knows whether it was the highest-priority requester, and thus

whether it is permitted to use the bus during the next cycle. Compared to cent-

ralized arbitration, this arbitration method requires more bus lines but avoids the

potential cost of the arbiter. It also limits the number of devices to the number of

request lines.

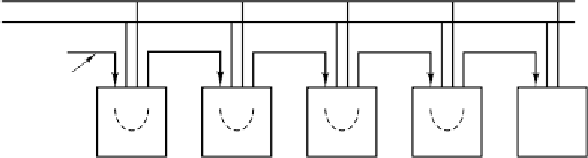

Another kind of decentralized bus arbitration, shown in Fig. 3-41, uses only

three lines, no matter how many devices are present. The first bus line is a wired-

OR line for requesting the bus. The second bus line is called

BUSY

and is asserted

by the current bus master. The third line is used to arbitrate the bus. It is daisy

chained through all the devices. The head of this chain is held asserted by tying it

to the power supply.

Bus request

Busy

V

CC

Arbitration

line

In Out

In Out

In Out

In Out

In Out

1

2

3

4

5

Figure 3-41.

Decentralized bus arbitration.

When no device wants the bus, the asserted arbitration line is propagated

through to all devices. To acquire the bus, a device first checks to see if the bus is

idle and the arbitration signal it is receiving,

IN

, is asserted. If

IN

is negated, it may

not become bus master, and it negates

OUT

.If

IN

is asserted, however, and the de-

vice wants the bus, the device negates

OUT

, which causes its downstream neighbor

to see

IN

negated and to negate its

OUT

. Then all downstream devices all see

IN

negated and correspondingly negate

OUT

. When the dust settles, only one device

will have

IN

asserted and

OUT

negated. This device becomes bus master, asserts

BUSY

and

OUT

, and begins its transfer.

Some thought will reveal that the leftmost device that wants the bus gets it.

Thus, this scheme is similar to the original daisy chain arbitration, except without

having the arbiter, so it is cheaper, faster, and not subject to arbiter failure.

Up until now, we have discussed only ordinary bus cycles, with a master (typi-

cally the CPU) reading from a slave (typically the memory) or writing to one. In

fact, several other kinds of bus cycles exist. We will now look at some of these.