Hardware Reference

In-Depth Information

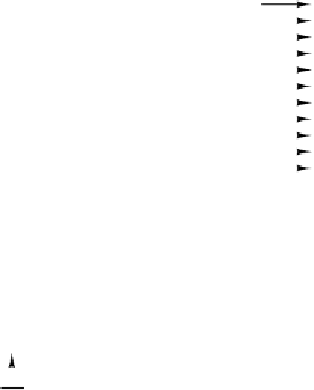

Two examples of 512-Mbit chips are given in Fig. 3-31. These chips have four

internal memory banks of 128 Mbit each, requiring two bank select lines to ch

oose

a bank. The design of

Fig.

3-31(a) is a 32M

16 design, with 13 lines for the

RAS

signal, 10 lines for the

CAS

signal, and 2 lines for the bank select. Together, these

25 signals allow each of the 2

25

×

internal 16-bit cells to

be

addressed. In contrast,

4 design, with 13 lines for the

RAS

signal, 12 lines for the

CAS

signal, and 2 lines for the bank select. Here, 27 signals can select any of the

2

27

internal 4-bit cells to be addressed. The decision about how many rows and

how many columns a chip has is made for engineering reasons. The matrix need

not be square.

Fig.

3-31(b) is a 128M

×

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

D0

D1

D2

D3

D4

D5

D6

D7

32M × 16

Memory

chip

128M × 4

Memory

chip

D0

D1

D2

D3

(512 Mbit)

A11

A12

(512 Mbit)

D8

D9

D10

D11

D12

D13

D14

D15

RAS

CAS

RAS

CAS

Bank 0

Bank 1

Bank 0

Bank 1

CS

WE

(a)

OE

CS

WE

(b)

OE

Figure 3-31.

Two ways of organizing a 512-Mbit memory chip.

These examples demonstrate two separate and independent issues for mem-

ory-chip design. First is the output width (in bits): does the chip deliver 1, 4, 8, 16,

or some other number of bits at once? Second, are all the address bits presented on

separate pins at once or are the rows and columns presented sequentially as in the

examples of Fig. 3-31? A memory-chip designer has to answer both questions be-

fore starting the chip design.

The memories we have studied so far can all be read and written. Such memo-

ries are called

RAM

s (Random Access Memories), which is a misnomer because

all memory chips are randomly accessible, but the term is too well established to