Hardware Reference

In-Depth Information

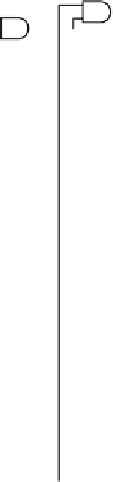

Data in

I

2

I

1

I

0

D

Q

D

Q

D

Q

Write

gate

Word 0

CK

CK

CK

Word 0

select

line

D

Q

D

Q

D

Q

Word 1

CK

CK

CK

Word 1

select

line

A

1

D

Q

D

Q

D

Q

A

0

Word 2

CK

CK

CK

Word 2

select

line

D

Q

D

Q

D

Q

Word 3

CK

CK

CK

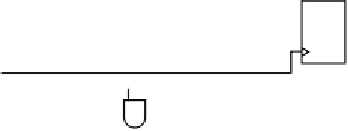

CS

•

RD

CS

O

2

RD

O

1

O

o

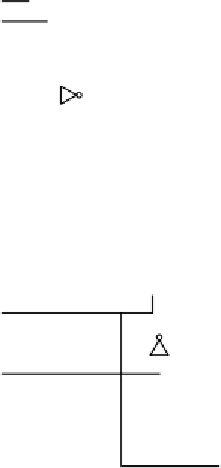

OE

Output enable = CS

•

RD

•

OE

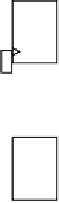

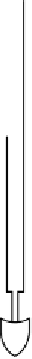

Figure 3-28.

Logic diagram for a 4 × 3 memory. Each row is one of the four

3-bit words. A read or write operation always reads or writes a complete word.

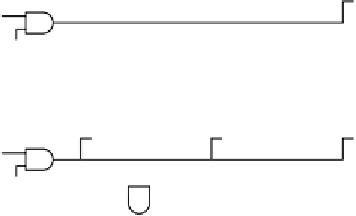

enabling one of the four write gates, depending on which word select line is high.

The output of the write gate drives all the

CK

signals for the selected word, loading

the input data into the flip-flops for that word. A write is done only if

CS

is high

and

RD

is low, and even then only the word selected by

A

0

and

A

1

is written; the

other words are not changed at all.