Hardware Reference

In-Depth Information

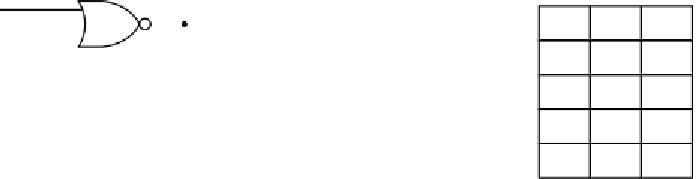

0

0

S

S

1

0

Q

Q

A

B

NOR

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

0

Q

Q

0

1

R

R

0

0

(a)

(b)

(c)

Figure 3-21.

(a)

NOR

latch in state 0. (b)

NOR

latch in state 1. (c) Truth table for

NOR

.

Q

, is 1. The 1 is fed back into the lower gate, which then has inputs 1 and 0, yield-

ing

Q

0. This state is at least consistent and is depicted in Fig. 3-21(a).

Now let us imagine that

Q

is not

0

but 1, with

R

and

S

still 0. The upper gate

has inputs of 0 and 1, and an output,

Q

, of 0, which is fed back to the lower gate.

This state, shown in Fig. 3-21(b), is also consistent. A state with both outputs

equal to 0 is inconsistent, because it forces both gates to have two 0s as input,

which, if true, would produce 1, not 0, as output. Similarly, it is impossible to have

both outputs equal to 1, because that would force the inputs to 0 and 1, which

yields 0, not 1. Our conclusion is simple: for

R

=

0, the latch has two stable

states, which we will refer to as 0 and 1, depending on

Q

.

Now let us examine the effect of the inputs on the state of the latch. Suppose

that

S

be

c

omes 1 while

Q

=

S

=

0. The inputs to the upper gate are then 1 and 0, forc-

ing the

Q

output to 0. This change makes both inputs to the lower gate 0, forcing

the output to 1. Thus, setting

S

(i.e., making it 1) switches the state from 0 to 1.

Setting

R

to 1 when the latch is in state 0 has no effect because the output of the

lower NOR gate is 0 for inputs of 10 and inputs of 11.

Using similar reasoning, it is easy to see that setting

S

to 1 when in state

Q

=

=

1

has no effect but that setting

R

drives the latch to state

Q

=

0. In summary, when

S

1, regardless of what state it

was previously in. Likewise, setting

R

to 1 momentarily forces the latch to state

Q

is set to 1 momentarily, the latch ends up in state

Q

=

0. The circuit ''remembers'' whether

S

or

R

was last on. Using this property,

we can build computer memories.

=

Clocked SR Latches

It is often convenient to prevent the latch from changing state except at certain

specified times. To achieve this goal, we modify the basic circuit slightly, as

shown in Fig. 3-22, to get a

clocked SR latch

.