Hardware Reference

In-Depth Information

In Fig. 3-1(b) two transistors are cascaded in series. If both

V

1

and

V

2

are

high, both transistors will conduct and

V

out

will be pulled low. If either input is

low, the corresponding transistor will turn off, and the output will be high. In other

words,

V

out

will be low if and only if both

V

1

and

V

2

are high.

In Fig. 3-1(c) the two transistors are wired in parallel instead of in series. In

this configuration, if either input is high, the corresponding transistor will turn on

and pull the output down to ground. If both inputs are low, the output will remain

high.

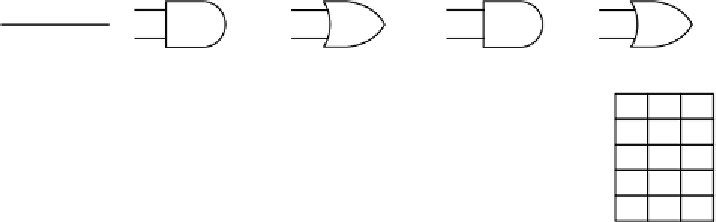

These three circuits, or their equivalents, form the three simplest gates. They

are called

NOT

,

NAND

, and

NOR

gates, respectively.

NOT

gates are often called

inverters

; we will use the two terms interchangeably. If we now adopt the conven-

tion that ''high'' (

V

cc

volts) is a logical 1, and that ''low'' (ground) is a logical 0,

we can express the output value as a function of the input values. The symbols

used to depict these three gates are shown in Fig. 3-2(a)-(c), along with the func-

tional behavior for each circuit. In these figures,

A

and

B

are inputs and

X

is the

output. Each row specifies the output for a different combination of the inputs.

NOT

NAND

NOR

AND

OR

A

A

A

A

A

X

X

X

X

X

B

B

B

B

A

X

A B X

0

A B X

0

A B X

0

A B X

0

0

1

0

1

0

1

0

0

0

0

1

0

0

1

1

0

1

0

0

1

0

0

1

1

1

0

1

1

0

0

1

0

0

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

(a)

(b)

(c)

(d)

(e)

Figure 3-2.

The symbols and functional behavior for the five basic gates.

If the output signal of Fig. 3-1(b) is fed into an inverter circuit, we get another

circuit with precisely the inverse of the

NAND

gate—namely, a circuit whose output

is 1 if and only if both inputs are 1. Such a circuit is called an

AND

gate; its sym-

bol and functional description are given in Fig. 3-2(d). Similarly, the

NOR

gate can

be connected to an inverter to yield a circuit whose output is 1 if either or both in-

puts are 1 but 0 if both inputs are 0. The symbol and functional description of this

circuit, called an

OR

gate, are given in Fig. 3-2(e). The small circles used as part of

the symbols for the inverter,

NAND

gate, and

NOR

gate are called

inversion bub-

bles

. They are often used in other contexts as well to indicate an inverted signal.

The five gates of Fig. 3-2 are the principal building blocks of the digital logic

level. From the foregoing discussion, it should be clear that

NAND

and

NOR

gates

require two transistors each, whereas the

AND

and

OR

gates require three each. For