Hardware Reference

In-Depth Information

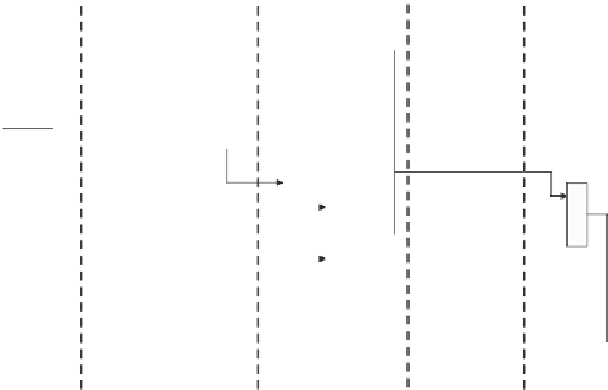

Execute (X)

Memory

Access (M)

Write

Back (W)

Instruction Fetch (F)

Instruction Decode/

Register Fetch (D)

M

U

X

+4

BZ

Bedingungs-

prüfer

M

U

X

M

U

X

M

U

X

$Y

A

L

U

Register-

bank

Daten-

speicher

$Z

Z

$X

Fetch

Buffer

Befehls-

speicher

Abbildung 3.9.

Implementierung einer Funf-Stufen-Pipeline mit Forwarding (fette

Leitungen, die von der X- und der M-Stufe zuruckfuhren) und Fetch Buffer

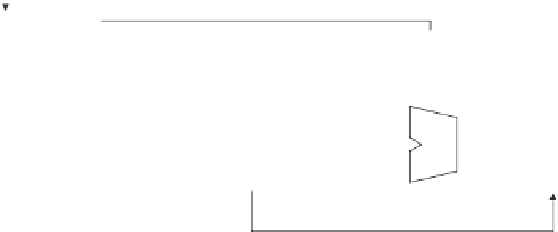

Takt

1

Takt

2

Takt

3

Takt

4

Takt

5

Takt

6

Takt

7

F

D

X

M

W

LDO $1,base,off

F

D

X

M

W

ADD $1,$1,2

F

D

X

M

SUB $3,$4,$5

Abbildung 3.10.

Read-After-Write-Abhangigkeit durch einen Ladebefehl. Auch Result

Forwarding kann den Stillstand der Pipeline fur mindestens einen Takt nicht vermeiden

3.2.3 Ablaufbedingte Hemmnisse

Auch die Ausfuhrung von bedingten Sprungbefehlen kann zum Aufhalten

der Pipeline fuhren. Man spricht von ablaufbedingten Hemmnissen (englisch:

Control Hazards

).

Ein bedingter Sprungbefehl besitzt zwei mogliche Nachfolgebefehle: Den un-

mittelbar folgenden Befehl und den als Sprungziel angegebenen Befehl. Wel-

cher der tatsachlich als nachster auszufuhrende Befehl ist, steht erst nach

der Ausfuhrungsphase (Execute) des Sprungbefehls fest, in der die Bedin-

gung gepruft wird (siehe Abbildung 3.1). Wenn ein bedingter Sprung von

der Fetch- in die Decode-Phase wechselt, wird bereits ein weiterer Befehl ge-

laden (Fetch). Dies kann aber nur einer der beiden potenziellen Nachfolger

sein. Dieser ist bereits dekodiert, wenn das Sprungziel endgultig fest steht.

Stellt sich heraus, dass der falsche Befehl geladen wurde, mussen sowohl der

nachste, bereits dekodierte und der ubernachste, bereits geladene Befehl ver-