Hardware Reference

In-Depth Information

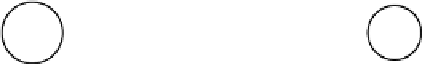

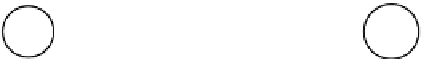

Read Hit

Read Hit

M

E

Write Hit

Write Hit

Write Miss

Read Miss

Write Hit

Write Miss

Read Miss

Read Miss

Write Hit/Miss

S

I

Read Miss

Read Hit

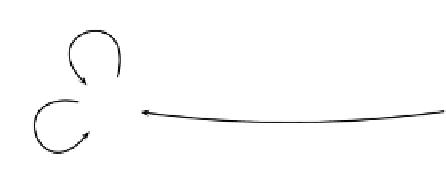

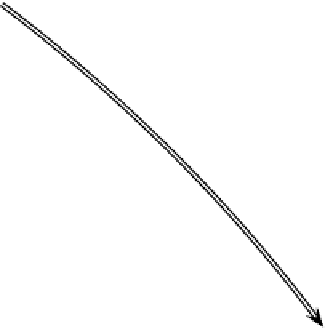

Abbildung 9.2.

Zustandsubergangsdiagramm des MESI-Protokolls fur einen

Write-Around Cache mit Write-Through . Doppelpfeile geben die Zustandsubergange an,

die durch einen Partnerprozessor initiiert werden. Der Ubergang von Modified nach Shared

wird beispielsweise durch den Lesezugriff eines Partners (bei dem dort ein Read Miss

auftritt) veranlasst. Die vielen moglichen Zustandsubergange von Invalid nach Invalid sind

nicht angegeben. Ausgehend von Invalid ist der Folgezustand bei einem Read Miss davon

abhangig, ob ein Partner meldet, dass er die Daten in seinem Cache hat oder nicht

Jeder Prozessor muss alle Speicherzugriffe auf den gemeinsamen Bus verfol-

gen, auch die des anderen Prozessors. Man nennt das

snooping

(schnuffeln).

Uber eigens dafur vorgesehene Signalleitungen auf dem Bus kann anderen

Prozessoren ggf. mitgeteilt werden, dass die Daten im eigenen Cache vorhan-

den sind. Falls die Daten im eigenen Cache verandert (

”

dirty“) sind, so wird

die entsprechende Cache Line zuruckgeschrieben und der Speicherzugriff des

anderen Prozessors solange unterbrochen.

Betrachten wir als Beispiel die Zustandsubergange beim Zugriff zweier Pro-

zessoren

P

1

und

P

2

auf eine Speicheradresse

a

. Keiner der Prozessoren habe

anfangs den Wert von Adresse

a

im Cache. Beide vermerken Zustand Invalid

(I) fur Adresse

a

. Dieser Zustand wird selbstverstandlich nicht gespeichert;

er gilt implizit fur alle nicht im Cache vorhandenen Daten.