Hardware Reference

In-Depth Information

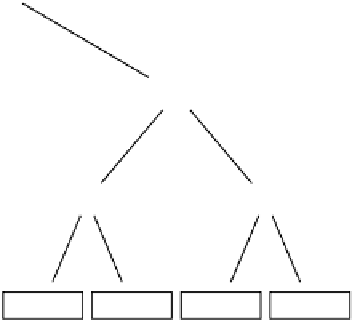

LRU-Bit 1

LRU-Bit 2

LRU-Bit 3

LRU-Bit 4

LRU-Bit 5

LRU-Bit 6

LRU-Bit 7

Block 0

Block 1

Block 2

Block 3

Block 4

Block 5

Block 6

Block 7

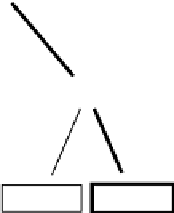

Abbildung 7.12.

Verdrangungsstrategie Pseudo-LRU bei einem 8-Wege assoziativen

Cache. Dargestellt sind die acht Blocke eines Sets sowie die Zuordnung von

Pseudo-LRU-Bits zu den sukzessive gebildeten Teilmengen. Die Nummerierung der Bits

beginnt dabei der Einfachheit halber links mit 1. Ist ein Pseudo-LRU-Bit 1, so erfolgte der

letzte Zugriff in die rechte darunterliegende Teilmenge. Fur eine Belegung der

Pseudo-LRU-Bits von (1

,

0

,

x

,

x

,

0

,

x

,

x

) ist das Aunden des zu verdrangenden Blockes

durch dicke Linien dargestellt. Die Werte der mit

x

gekennzeichneten Bits sind im

Augenblick ohne Bedeutung (so genannte don't care Werte)

wird also Bit 1 zu 0, Bit 2 zu 1 und Bit 5 zu 1 gesetzt. Der Vektor andert

sich also zu (0

,

1

,

0

,

1

,

1

,

1

,

1). Wir sehen auch, dass in diesem Fall die Werte

der nicht betrachteten Bits drei, vier sowie sechs und sieben ohne Bedeutung

sind (don't care-Werte).

Ubung 7.2.3

Fur welche Werte der Assoziativitat sind die Verdrangungs-

strategien LRU und Pseudo-LRU identisch?

7.2.3

Ubung 7.2.4

Erganzen Sie die folgende Tabelle fur einen 8-Wege assoziativen

Cache (die Belegung der LRU-Bits in der ersten Spalte muss nicht unbedingt

die Folgebelegung der vorangegangenen Zeile sein!):

7.2.4