Hardware Reference

In-Depth Information

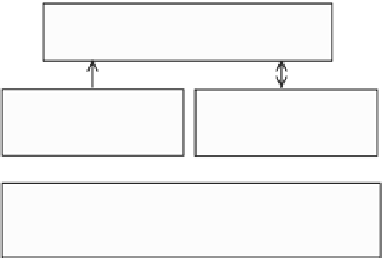

Prozessor

First-Level Cache

für Befehle

First-Level Cache

für Daten

Second-Level Cache

(Befehle und Daten)

Hauptspeicher

Abbildung 7.9.

Typische Speicherhierarchie mit zwei Ebenen von Caches. Aufgrund der

getrennten First-Level-Caches fur Befehle und Daten spricht man von einer

Pseudo-Harvard-Architektur

meist nicht besonders groß. Darunter kann ein

Second-Level-Cache

vorhan-

den sein, der zwar langsamer als der First-Level-Cache ist, aber immer noch

deutlich schneller als der Hauptspeicher. Er ist großer als der First-Level-

Cache. Zwischen dem Hauptspeicher und dem Second-Level-Cache konnte

noch ein Third-Level-Cache angeordnet sein usw. Beim Zugriff auf Daten

kann in allen Hierarchie-Ebenen gleichzeitig begonnen werden, die Daten zu

suchen.

Aus Sicht eines Betriebssystems sind auch der Hauptspeicher sowie die Fest-

platten Teil der Speicherhierarchie.

Es hat sich durchgesetzt, den First-Level-Cache in zwei Teile zu trennen:

Einen fur Daten und einen fur Befehle. Der Prozessor greift auf den Befehls-

cache ausschließlich lesend zu. Diese Aufteilung ist bekannt unter dem Begriff

Pseudo-Harvard-Architektur

. Im Unterschied dazu verfugt die klassische von-

Neumann-Architektur uber einen gemeinsamen Speicher fur Programm und

Daten. Die Vorsilbe

”

Pseudo“ deutet an, dass die Aufteilung in getrennte

Speicherbereiche fur Programm und Daten erst in einer sehr hohen Ebene

der Speicherhierarchie geschieht. Eine reine Harvard-Architektur wurde auch

getrennte Hauptspeicher fur Programm und Daten aufweisen. Eine solche

Architektur findet man lediglich bei Signalprozessoren.

Ubung

7.2.1

Warum ist es bei den meisten modernen Prozessoren verbo-

ten, Programme zu schreiben, die sich selbst verandern (so genannter selbst-

modifizierender Code)?

7.2.1