Hardware Reference

In-Depth Information

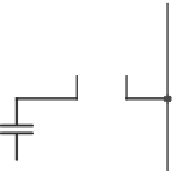

Zeilenleitung (Select)

Spalten-

leitung

(Bit)

Abbildung 7.1.

Zwei ROM-Speicherzellen: links mit elektrischer Verbindung von Zeilen-

und Spaltenleitung, rechts ohne

Zeilenleitung (Select)

Spalten-

leitung

(Bit)

Masse

Abbildung 7.2.

Aufbau einer dynamischen Speicherzelle (DRAM) aus einem Transistor

und einem Kondensator

tenleitung auf. Mit dieser Technik lassen sich auch einmalig programmierbare

Festwertspeicher realisieren, so genanntes

Programmable ROM

(PROM). Bei

der Fertigung sind zunachst alle Dioden vorhanden. Es konnen Dioden durch

Anlegen einer sehr hohen Spannung gezielt zerstort werden. Eine Umpro-

grammierung ist danach nicht mehr moglich.

Ferner gibt es Festwertspeicher, die sich durch Bestrahlung mit UV-Strahlen

wieder loschen lassen. Die gangigsten wiederbeschreibbaren Festwertspeicher

sind derzeit so genannte

Flash-ROM-

Bausteine. Diese konnen elektrisch ge-

loscht und neu beschrieben werden. Allerdings ist dieser Speicher relativ lang-

sam und lasst sich nur maximal eine Million Mal neu beschreiben. Daher lasst

sich dieser Speicher nicht als Hauptspeicher einsetzen.

7.1.2 Dynamisches und statisches RAM

Es gibt zwei Arten von RAM: dynamisches und statisches (kurz DRAM und

SRAM). Dynamische Speicherzellen enthalten lediglich einen Transistor und

einen Kondensator, wie in Abbildung 7.2 dargestellt. Der Zustand der Spei-

cherzelle wird durch die Ladung dieses Kondensators beschrieben (z.B. Kon-

densator geladen

.

=1,entladen = 0). Beim Auslesen der Zelle geht die La-

dung verloren. Die Zelle muss also anschließend wieder aufgeladen werden

(destruktives Lesen).