Hardware Reference

In-Depth Information

69

68

67

66

65

64

63

1 Adressbit

2 Adressbits

3 Adressbits

62

61

1

2

3

4

5

6

7

8

Anzahl Historybits

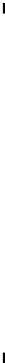

Abbildung 6.6.

Messergebnisse fur die Trefferrate des Quicksort-Programms fur steigende

Lange des Schieberegisters (Historybits) und unterschiedliche Anzahl Adressbits

on“. Ab da bleibt er unverandert. In diesem Beispiel werden also nach einer

Einschwingphase alle Verzweigungen korrekt vorhergesagt.

Abbildung 6.6 zeigt Messergebnisse fur die Trefferrate des Quicksort-Pro-

gramms fur steigende Lange des Schieberegisters (Historybits) und unter-

schiedliche Anzahl Adressbits. Auch hier arbeitet die Sprungvorhersage um-

so besser, je genauer die Pradiktion einzelnen Adressen zugeordnet werden

kann. Mehr als drei Historybits sind kaum lohnend, wirken sich teilweise so-

gar negativ aus, wie der obersten Kurve fur drei Adressbits zu entnehmen

ist.

6.5

6.5 Implementierungsaspekte

Damit die Sprungverzogerung moglichst gering wird, ist es erforderlich, dass

die Sprungvorhersage in einer moglichst fruhen Pipeline-Stufe stattfindet.

Bei der Funf-Stufen-Pipeline muss das Sprungziel bereits am Ende der Fetch-

Phase bekannt sein, damit im nachsten Takt der vorhergesagte Befehl geladen

werden kann und keine Sprungverzogerung auftritt. Das bedeutet, dass das

Sprungziel bekannt sein muss, bevor der Befehl dekodiert ist.

Eine Moglichkeit ist ein so genannter

Branch-Target-Buffer

, der in die Logik

fur den Instruction Fetch integriert wird [17]. Dieser enthalt zu 2

i

Befehls-

adressen die Adresse des Folgebefehls. Dabei treten Mehrdeutigkeiten auf,