Hardware Reference

In-Depth Information

are met, the device will jump to ISR(SPI_STC_vect). ISR(SPI_STC_vect) is similar to a function, but has some key

differences. The compiler does not see this as a normal function, so code may be optimized on compile. To protect

against this, data types may have the property

_volatile

added when in doubt. The biggest difference is that nothing

may be passed to an ISR upon calling it and no data will be returned. ISR cannot call as a normal function; only the

internal interrupt handler may call it when conditions are met. Global variables can be used within the ISR and will be

usable upon exit. Otherwise, using memory space and pointers is also an option, though greater in complexity.

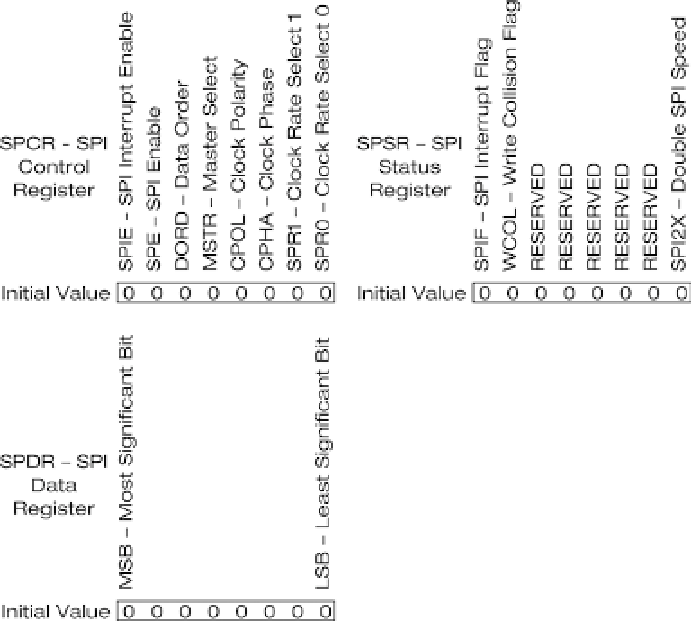

SPI by the Registers

There is no library functionality for an Arduino to run as a slave device at the time of writing. You can create a slave

by directly addressing the registers that control SPI. This method will be used in Listing 10-2 to create a slave device

and will be used in subsequent examples. The functionality of SPI is controlled within three 8-bit registers. This does

not include manipulating the data direction registers or the SREG for global interrupts, which will also be required

for a proper SPI device to be written in a register. The three SPI registers are the SPCR (SPI control register), SPSR (SPI

status register), and SPDR (SPI data register). The layouts of these three registers are shown in the Figure

10-1

.

Figure 10-1.

SPI register structure

The SPIE (SPI interrupt enable) in the SPCR enables the SPI interrupt vector when SREG is also enabled. This

allows the device to respond quickly when data is ready to transmit and is an absolute must for a slave device. SPI is a

highly time-sensitive protocol; the master will transmit data when it is ready and assumes that the slave is waiting. The

slave cannot delay the master and will cause problems when not properly synchronized with the master. It is possible

for the slave to begin listening to the transmission partway through, which will result in lost data. In addition to using

interrupts, the master may also include a short delay before the first byte in a string of bytes is transmitted, which

helps ensure that the slave is ready and waiting.