Biomedical Engineering Reference

In-Depth Information

3.3.2 Functional Blocks of a Digital ECG Acquisition

System

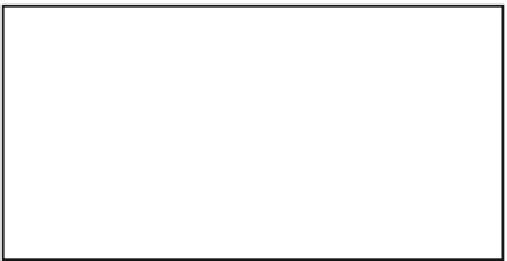

The generalized block diagram of a digital ECG acquisition hardware module is

shown in Fig.

3.1

. It can be divided into three functional blocks connected in

sequence, viz., analog front end, AD conversion, and a processor with a bus

interface capability. The function of the analog front end is to reject (or at least

minimize) the artifacts associated with the biosignal at the input, amplify the

biosignal to the input span of the AD converter, and maintain galvanic isolation of

the patient from power line or any accidental transient voltage surge.

The first stage of the analog front end is patient isolation circuit, which prevents

any current from the acquisition circuit to flow through the patient body. The first

stage provides low offset, high CMRR instrumentation amplifier (INA). This is the

most important of the circuit since it determines the quality of the acquired signal.

The next stage is a low pass filter and a notch filter to block high frequency and

power line interference. If the AD converter is operated in unipolar mode of

operation, then a level shifter is included at the final stage of analog conditioning.

The output from this stage is 0-5 V. Today's ECG acquisition cards employ a

12- or 16-bit AD converter, which supplies the quantized samples to the high-end

microcontroller. The microcontroller provides some intelligent features to the

acquisition module like self-test, auto-calibration. However, its main function is to

deliver the data samples to the bus interface unit for delivery to the final storage

device, which may be a computer, personal digital assistant, mobile phone, iPad,

etc. For this, the microcontroller is provided with a small buffer memory and

associated peripherals. A graphical front end at the acquisition device may provide

some flexibility in selecting the sampling rate, duration of acquisition, etc.

Lead

system

Isolation Circuit

High end

Microcontroller

with bus

interface

Computer,

mobile

phone, PDA

etc for

acquisition

AD

Converter /

Quantizer

Instrumentation

Amplifier

Filter

Section

ECG acquisition module

Fig. 3.1

Block diagram of a digital ECG acquisition module

Search WWH ::

Custom Search