Hardware Reference

In-Depth Information

b

a

V

DD

V

DD

Nominal

V

DD

Nominal

Pass

Pass

Vmin

Vmin

Fail

Fail

0

5

10

15

20

0

5

10

15

20

Period (ns)

Period (ns)

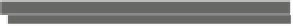

Fig. 2.18

Shmoo plots of a combinational CMOS circuit with a bridging defect: (

a

) Defect-free

case and (

b

) defective case (

Rodrıguez-Monta nes

2006

)

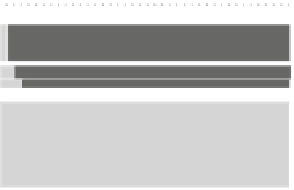

Fig. 2.19

Shmoo plots for

two inverters with their

outputs bridged together

.Rb D 1 k/. Each inverter

belongs to a different inverter

chain

(

Rodrıguez-Monta nes

V

DD

V

DD

Nominal

Fail

Vmin

Pass

0

5

10

15

20

Period (ns)

p-bridged networks a shmoo plot like the one in Fig.

2.19

is obtained (

Rodrıguez-

Montanes et al.

2006

). In this particular example, the bridge is connecting the output

of the inverters.

The main drawback of this technique is the number of ATE measurements re-

quired. Each individual measurement performed on the ATE can result in a pass-fail

(e.g. of a functional test) or in a numerical result (e.g. failure counts or bit error rate).

Some approaches have been proposed to reduce the time required to generate

Shmoo algorithm that extracts the device characteristics from a minimum number

of coordinate points that actually have to be measured. This algorithm reduces the

Shmoo execution time significantly.

2.3.3.5

Temperature Based Testing Techniques

Temperature may also give additional information to detect bridges which are

not observable at nominal conditions. Resistive bridges are temperature sensi-

tive because their electrical resistance varies with temperature (

Semenov and

ture coefficient (RTC) such as metals and polysilicon increase their resistance