Hardware Reference

In-Depth Information

Vn

1

is interpreted as a logic '0' if it is smaller than the gate 'c' logic threshold

Vth

c

.A

defective effect

appears on the output of gate 'c' and is propagated to the

primary output of the circuit.

Vn

1

is interpreted as a logic '1' if it is higher than the gate 'c' logic threshold

Vth

c

.A

defect-free effect

appears on the output of gate 'c' and is propagated to

the primary output of the circuit.

This small example highlights that the bridge defect may be detected or not by

a given test vector depending on the value of the intermediate potential Vn

1

.This

potential depends on the technological and topological transistor parameters of Gate

'a' (C

ox

,V

T

,

P

,W

P

,L

P

:::) but also on the value of the bridge resistance Rsh. As

the bridge resistance value is obviously an unpredictable parameter, it is not possible

to compute the intermediate voltage Vn

1

. Consequently it is not possible to predict

the effect of the defect.

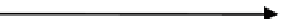

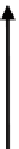

However, it is possible to analyze the impact of the bridge resistance value on

through electrical simulations. Two distinct regions can be distinguished according

to the Rsh value. In the high resistance range, the bridging defect does not modify

the logical behaviour and the circuit operates as a defect-free circuit. In the low resis-

tance range, the bridging defect induces a Vn

1

value smaller than the logic threshold

Vth

c

of the driven gate 'c' and this value is logically interpreted as a defective '0'.

The frontier between these two regions corresponds to a

critical resistance

value

R

C

. It is worth noting that although the bridge resistance value is an unpredictable

Vn

1

5

Vth

c

0

R

C

R

C

Rsh

Vn

3

5

0

R

C

R

C

Rsh

Out

5

0

R

C

R

C

Rsh