Hardware Reference

In-Depth Information

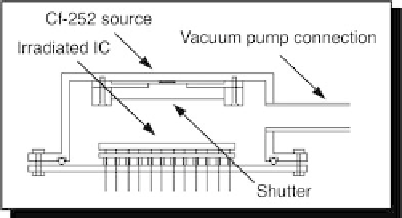

Fig. 8.11

Cross-sectional

view of the miniature vacuum

chamber

to compare these techniques by running experiments on the same testbed architec-

ture and a common test scenario. The results of these experiments are presented in

8.3.2.1

Heavy-Ion Radiation

The fault injection experiments with heavy-ion radiation (HI, for short) were carried

out at Chalmers University of Technology in Goteborg, Sweden. A Californium-252

source can be used to inject single event upsets, i.e., bit-flips at internal locations

of a target IC using a miniature vacuum chamber. Figure

8.11

depicts the cross-

sectional view of the miniature vacuum chamber. The pins of the target IC are

extended through the bottom plate of the vacuum chamber, so that the chamber

with the circuit can be directly plugged into the socket of the circuit under test. The

vacuum chamber contains an electrically controlled shutter, which is used to shield

the circuit under test from radiation during bootstrapping.

A major feature of the HI injection technique is that faults can be injected into

VLSI circuits at locations that are difficult (and mostly impossible) to reach by other

techniques. The transient faults produced are also reasonably well spread at random

locations within an IC, as there are many sensitive memory elements in most VLSI

circuits. As device feature size of integrated circuits is shrinking, radiation induced

bit-flips, also known as

soft errors

, constitute an increasingly important source of

The percentage of multiple bit errors induced in the main registers was found to be

8.3.2.2

Pin-Level Fault Injection

The experiments with the pin-level fault injection technique were conducted at

LAAS-CNRS, in Toulouse, France using the MESSALINE tool. Figure

8.12

de-

picts the principle of the pin-forcing technique (PF). In this case, the fault is directly

applied on the pin(s) of the target IC.