Hardware Reference

In-Depth Information

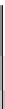

V

DD

PMOS

pull-up

network

charging

(0

half of energy dissipated as heat

→

1)

Input

Output

load

capacitance

C

L

NMOS

pull-down

network

discharging

(1 → 0)

energy dissipated as heat

Fig. 7.1

Dynamic switching power

Dynamic power is divided into

dynamic short-circuit

power and

dynamic switch-

ing

power. Dynamic short-circuit power is due to the direct current path from V

DD

to G

ND

that occurs during output switching. The short-circuit current of a CMOS

logic gate is proportional to the ratio between the input slew of the gate and the load

capacitance at the output of the gate. The short-circuit power represents a small

fraction of the total dynamic power and is often neglected.

Dynamic switching power is due to charging and discharging of the output

load capacitance during switching. Let us consider the generic representation of

Q

D

C

L

:V

DD

is delivered to the load capacitance C

L

. The power rail must supply

this charge at voltage V

DD

, so the energy supplied is Q:V

DD

D

C

L

:V

DD

.However,

the energy E stored on a capacitance C

L

charged to V

DD

is only half of this, i.e.,

E

D

1=2:C

L

:V

DD

. According to the energy conservation principle, the other half

must be dissipated by the PMOS transistors in the pull-up network. Similarly, when

the inputs change again causing the output to discharge (from 1 to 0), all the en-

ergy stored on the capacitance C

L

is dissipated in the pull-down network, as no

energy can enter the ground rail .Q:V

GND

D

Q:0

D

0/. In both cases, the energy is

dissipated as heat

(

Athas et al.

1994

).

The dynamic switching power is consumed during the charge of the load ca-

pacitance C

L

, when a current I flows between power and ground rails through

the capacitance. The power consumed during the time interval Œ0; T is therefore:

P

dyn

D

V

DD

:I

D

V

DD

:Q:1=T where Q

D

C

L

:V

DD

. As several transitions may oc-

cur during the time interval Œ0; T , the dynamic switching power consumption can

be expressed as follows:

P

dyn

D

C

L

:V

DD

:N

0!1

:1=T

(7.1)

Where N

0!1

represents the number of rising transitions at the gate output during

the time interval Œ0; T . Without loss of generality, it can be assumed that the number

of rising transitions is equal to half of the total number of N transitions at the gate