Hardware Reference

In-Depth Information

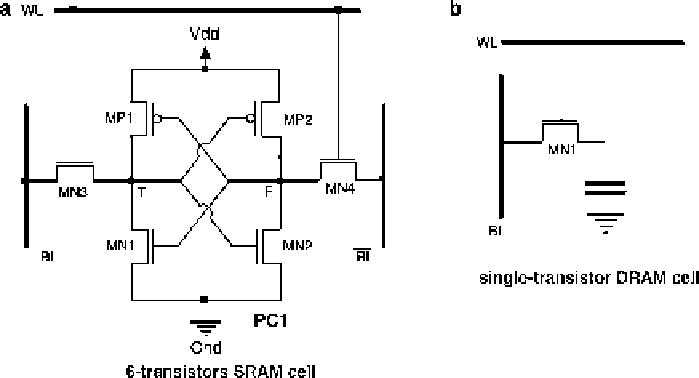

Fig. 6.3

(

a

)SRAM,and(

b

) DRAM device level structural model

due to both their peculiar goals and the amount of available details. Several types

of users can be considered in the supply chain of semiconductor memories: the

designer, the test engineer, the device manufacturer, the system integrator, and

the end-users.

Faults and defects

: defines the classes of failure mechanisms as well as physical

defects that may occur in a given memory. They will be deeply analyzed in the

next sections.

6.3

Models for Structures, Behaviors, and Architectures

Dealing with the multidimensional space presented in the previous section is always

a complex and hard to manage task. Appropriate sub-spaces, or views, are therefore

used to reduce the complexity of the modeling process.

Van de Goor

(

1991

)pro-

from the external levels to the internal ones, the amount of information about the ac-

tual implementation of the memory decreases while the information about the way

the system is expected to work increases. This sub-space has the main disadvantage

of mixing, at the same time, abstraction levels and representation domains.

Here we prefer to introduce a different sub-space that explicitly considers the

dimensions. Figure

6.5

shows this sub-space where for the sake of simplicity only

the most representative representation domains are included. Based on this model, in