Hardware Reference

In-Depth Information

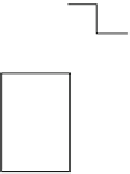

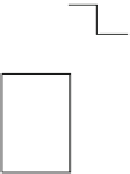

Fig. 5.4

Example of aliasing

in diagnosis. The response to

a test set in (

a

) is explained

by a single stuck-at fault. The

defective behavior is actually

more complex because the

additional test in (

b

) produces

a 0 at the output

a

Test set detects all single stuck-at faults:

1 0 1 1

a

&

0 1 0 1

b

x

=1

x 1

1 1

1

1 0 1 0

c

&

1 1 0 1

d

Possible

explanation

b

Improved test set:

a

1 0 1 1 0

a

&

0 1 0 1 1

b

=1

x 1

1 1

1 0

1 0 1 0 1

c

&

d

1 1 0 1 0

d

Possible

explanation

The first part of the condition is true, if there is an event on line a, and the second

part is true, if the final value of a is different from the current value of line b.

At the first glance, the explanations for observed responses with the minimum

number of CLFs are the most reasonable ones, however, there is the risk of alias-

complexity of their conditions should be considered.

In most cases, the goal for production test generation is to achieve high stuck-

at fault coverage. It is likely, that standard ATPG would generate the four patterns

shown in case (a). This test set provides complete single stuck-at fault coverage and

leads to two fails. The most reasonable explanation of this behavior is a stuck-at 1

at the output x. However, if one additional pattern is added to the test set like in

case (b), the circuit produces a 0. This response cannot be explained anymore by a

stuck-at fault at the output. In fact, there exists no single stuck-at fault, which would

produce such a response. One possible explanation involves two stuck-at faults at

lines a and d .