Hardware Reference

In-Depth Information

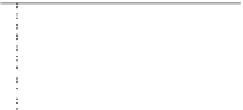

Fig. 4.3

Critical resistances

in circuit from Fig.

4.2

for

fault-site input combinations

0011 (

solid lines

) and 0111

(

dashed lines

)

intermediate voltage V

0

. This voltage will be lower under FSIC 0111 compared to

FSIC 0011, because only one p-transistor in the NAND gate A is pulling up the

voltage to V

DD

. (Speaking colloquially, one could say that the logic-1 value on a is

driven with less strength.)

A bridging defect with non-zero resistance leads to voltages V

a

and V

b

on lines a

and b with V

a

>V

b

. The difference V

a

>V

b

is larger for larger values of R

sh

.Pos-

the characteristics for FSIC 0011 (solid lines) are located above their counterparts

for vector 0111 (dashed lines), due to the different numbers of the active transistors

in gate A.

The intermediate voltages are interpreted by subsequent logic gates as either

logic-1 or logic-0, depending on the

logic thresholds

of these gates. (It is also pos-

sible to consider an intermediate voltage region in which no definite logic value is

driven by the bridged lines a and b are shown in Fig.

4.3

as horizontal lines because

they are independent of the bridge resistance R

sh

. In general, a gate will interpret

different logical values for different bridge resistances. Consider gate C under FSIC

0011. Bridge resistance R

C

, given by the crossing of

Th

C

and the solid characteris-

tic V

a

, is called

critical resistance

of gate C under FSIC 0011. For all R

sh

2

Œ0; R

C

,

gate C interprets logic-0, while for all other bridge resistances it interprets logic-1.

Since logic-0 is the erroneous value, [0, R

C

] is called the (local) ADI at the (second)

input of gate C . We write [0, R

C

] 0/1 to denote that the logical value on the line is

0ifR

sh

is within the ADI and 1 otherwise.

The local ADI depends both on the logic threshold of the gate and the FSIC. For

gate C and FSIC 0111, the local ADI would be [0, R

C

0

]. For gate D and FSIC 0011,

Th

D

and V

a

.R

sh

/ do not cross; there is no critical resistance and the local ADI is

empty, i.e., the fault-free logical value is interpreted for all possible bridge resis-

tances. Under vector 0111, a critical resistance (R

D

0

) exists, and the local ADI is