Information Technology Reference

In-Depth Information

gates. He also showed analytically how a NAND MUX architecture can be used

to enhance the reliability of a system in the presence of limited computation noise

and large bundle size (N). Bundle size (N) is defined as the number of replicated

transmission lines and redundancy factor (R) is defined as the ratio of the circuit

sizes of the redundant and nonredundant designs for a nanosystem. Note that R is

dependent on the value of N. Reliability evaluation of multiplexing (MUX)

architectures is based on PMC technique discussed earlier in this chapter.

Von Neumann addressed a fundamental problem in his seminal work [47], the

problem that the probability (

d

) of malfunction of a system cannot be less than

probability (

e

) of failure of the last device in the design. He proposed multiplexing

(MUX) as a technique to achieve

d

e

. The main trick behind MUX is in replacing

a single transmission line by a bundle of N parallel transmission lines. Since a

signal bundle is used to carry messages, a single logic gate is replaced by N copies.

The N devices process the signals in parallel to give N outputs. Each element of the

output set will be identical and equal to the original output of the logic gate, if all

the copies of the inputs and devices are reliable. However, if the inputs or devices

are in error, the outputs will not be identical. To tackle such an error-prone

scenario, von Neumann defined a critical level

D 2ð

0

o

5

Þ

. The output of the

MUX unit is considered stimulated (taking logical value true) if at least

ð

1

DÞ

N of the outputs are stimulated and non-stimulated (taking logical value

false) if no more than

D

N outputs are stimulated. Any other number of

stimulated lines is interpreted as a malfunction.

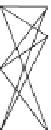

The MUX unit formed by the signal bundles and logic gates is known as the

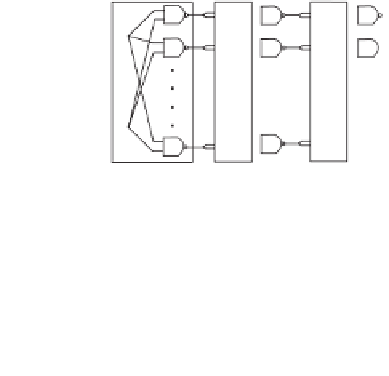

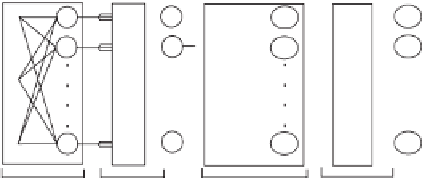

executive stage since this performs the basic logic function. In Figure 10.11, the

executive stage of the NAND and MAJ MUX consist of N NAND and MAJ

gates, respectively. The advantage of implementing this technique at the gate level

is to increase the reliability of the basic building blocks of a logic network, hence,

enhancing the reliability of more complex units built from these.

In [47], von Neumann observed that for MAJ MUX whose outputs are

governed by a two-to-one majority of the input bundles (two inputs are either

stimulated or non-stimulated while the third one represents a different logic state),

the error at the output bundle is the sum of errors in two governing input bundles.

;

0

:

(K

1

)

(K

2

)

(K

3

)

(K

0

)

X

M

M

X

M

M

X

M

M

M

M

Y

Y

(K

1

)

Y

M

M

M

Z

Z

M

U

U

U

Executive stage

Restorative stage

Executive stage

Restorative stage

Executive stage

Restorative stage

(a)

(b)

Figure

10.11.

Original von Neumann MUX schemes.

Search WWH ::

Custom Search