Information Technology Reference

In-Depth Information

x1

y1

y1

x1

y1

1 bM

x1

MG

X1

MG

Y1

MG

Z1

MG

x2

y2

x2

y2

x2

y2

Z

1 bM

MG

MG

X2

Y2

MG

Z2

MG

MG

1 bM

X3

MG

Y3

MG

Z3

MG

x3

x3

x3

y3

y3

y3

1 bM

MG = Majority gate

MG

MG = Majority gate

(a)

(b)

Figure

10.2.

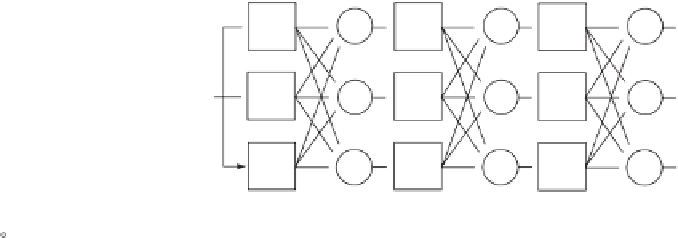

Different CTMR configurations. (a) Generic CTMR: multilayer voting;

(b) CTMR with triple voters: smaller granularity.

with a MAJ gate. Figure 10.2a shows a first-order CTMR configuration where the

parallel processing units in each of the three TMR units are NAND gates. Due to

the area and latency overheads associated with this technique, the triplicated units

in the CTMR with a multilayer voting scheme are normally functional units or

logic blocks, not single gates as shown in Figure 10.2a. Since the triplicated

functional units or logic blocks may consist of a large number of gates, their

failure probability is more than individual gates. Hence, the multilevel CTMR

with triple voters as shown in Figure 10.2b may be used to apportion the system

into optimally sized functional units or logic blocks to effectively allow the

architecture to withstand more errors across the triplicated units [14].

10.2.1.3. Triple Interwoven Redundancy (TIR).

The idea of TIR is based

on von Neumann's multiplexing techniques and interwoven redundant logic [15].

A TIR architectural configuration has three times as many gates and interconnects

as compared to the nonredundant network. The interconnections are arranged in

random patterns. Such inherent randomness in the interconnections makes this

structural redundancy technique favorable for the integration of molecular

devices, since the manufacturing method for such devices is most likely to be

stochastic chemical assembly. Figure 10.3 shows a nonredundant half adder and

its corresponding TIR implementation. For a particular interconnect pattern, [16]

shows that the TIR actually works as a TMR configuration, implying that TMR is

a specific implementation of TIR.

10.2.1.4. Multiplexing Techniques.

Structural redundancy-based architec-

tures that can circumvent transient faults can affect both the computation and

communication in nanosystems. Interestingly, von Neumann addressed this issue

Search WWH ::

Custom Search