Information Technology Reference

In-Depth Information

7.4. SPIN-WAVE RECONFIGURABLE MESH

A nanoscale spin-wave reconfigurable mesh of size N

2

consists of an N

N array

of processors connected to a reconfigurable spin-wave bus grid, where each

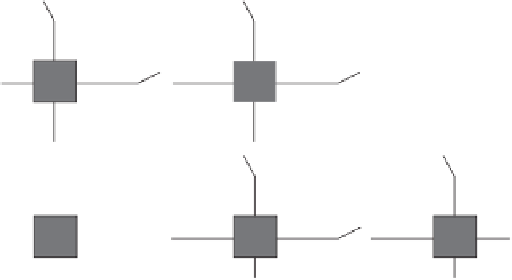

processor has a locally controllable bus switch [12], as shown in Figure 7.5.

In the proposed spin-wave reconfigurable mesh architecture with spin-wave

buses, a set of column spin-wave buses on the bottom and a set of row spin-wave

buses on the top are connected via the spin-wave switches. Each switch is placed at

the grid point of the mesh, as shown in Figure 7.6. Basically, the nanoscale spin-

weave reconfigurable mesh is similar to the standard reconfigurable mesh, except

for the spin-wave buses and switches.

It is worth noting that, similar to the standard reconfigurable mesh, the

nanoscale reconfigurable mesh of size N occupies N

N area, under the assump-

tion that processors, switches, and the link between adjacent switches occupy unit

area. However, the main difference in terms of area here is that the unit of area is

at nanoscale level as opposed to the standard reconfigurable meshes that are at

microscale level of integration.

Each of the spin-based devices serves as a one-bit input/output port. One spin-

wave packet excited by one port can be superposed with many packets generated

by the nearby ports. The length of interaction among the spin-based devices is

limited by the spin-wave attenuation caused mainly by the scattering on phonons.

The length of interaction is defined by the material properties of the ferromagnetic

film, film size, and the operation temperature. According to our experimental data

it can be as high as tens of microns.

i

1

, j

1

+

+

i, j

+

1

i

−

1

, j

+

1

“On”

Spin wave switch

i

−

1

, j

i, j

i

+

1

, j

“Off”

100 nm

Spin-based device

100 nm

i

+

1

, j

−

1

i, j

−

1

i

−

1

, j

−

1

Spin wave bus

Figure

7.5.

Reconfigurable mesh architecture.

Search WWH ::

Custom Search