Hardware Reference

In-Depth Information

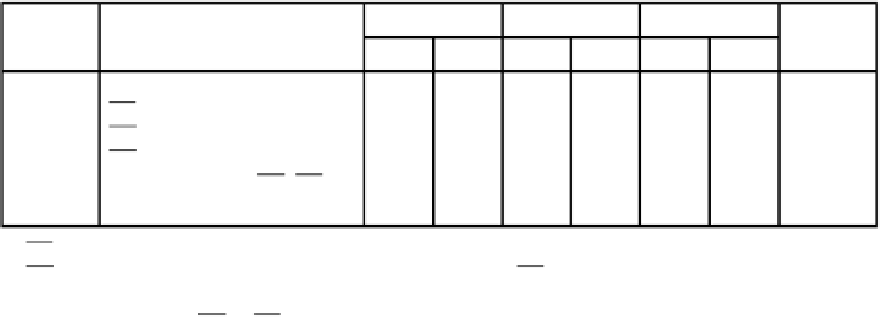

assuming that the CE and OE signals have been valid (low) before the required moment (

t

CE

or

t

OE

ns before data become valid). After address change, the data value will change immediately

(data hold time is 0). The values of read timing parameters are listed in Table 14.11.

AT28C010-12

AT28C010-15

AT28C010-20

Symbol

Parameter

Unit

Min

Max

Min

Max

Min

Max

t

ACC

t

CE

(1)

t

OE

(2)

t

DF

(3),(4)

t

DH

Address to output delay

CE to output delay

OE to output delay

OE to output float

Output hold from OE, CE

address, which occurred first

120

120

50

50

150

150

55

55

200

200

55

55

ns

ns

ns

ns

ns

0

0

0

0

0

0

0

0

0

1. CE may be delayed up to

t

ACC

2

t

CE

after the address transition without impact on

t

ACC

.

2. OE may be delayed up to

t

CE

2

t

OE

after the falling edge of CE without impact on t

CE

or by

t

ACC

2

t

OE

after an

address change without impact on

t

ACC

.

3.

t

DF

is specified from OE or CE, whichever occurs first (C

L

5

5 pF).

4. This parameter is characterized and is not 100 percent tested.

Table 14.11

■

AT28C010 read characteristics

The write cycle timing diagram is shown in Figure 14.40. There are two write timing

diagrams: WE-controlled and CE-controlled diagrams, depending on which signal is asserted the

latest. In a WE-controlled write timing waveform, the CE signal is asserted (goes low) earlier than

the WE signal and becomes inactive (goes high) after the WE signal goes high. In a CE-controlled

write cycle, the WE signal goes low earlier and returns to high later than the CE signal. In Figure

14.40, the control signal that is asserted the latest must have a minimal pulse width of 100 ns.

The address input must not be valid after the assertion (going low) of the latest control signal and

must remain valid for at least 50 ns after the assertion of the same signal. The values of write

cycle timing parameters are shown in Table 14.12. The write data must be valid at least 50 ns

before the latest control signal starts to rise. The write data need not be stable after the latest

control signal (data hold time) rises.

The page-mode write cycle timing diagram is shown in Figure 14.41, and the values of the

timing parameters are shown in Table 14.13.

The write timing waveform illustrates only how the CPU writes data into the EEPROM.

The EEPROM still needs to initiate an internal programming process to write data into the

specified location. The CPU can find out whether the internal programming process has been

completed by using the data polling or the toggle bit polling method.

One can choose to use or not to use expanded memory (paging) when adding external mem-

ory chips to the HCS12, but being limited to adding less than 64 kB of external memory with-

out using expanded memory doesn't make much sense. When expanded memory is used, we

can add up to 1 MB of external memory if the on-chip flash memory is disabled. The external

memory can be 8 or 16 bits wide. In an 8-bit-wide external memory, the HCS12 performs two

read bus cycles when handling 16-bit data. This reduces the external memory performance to

Search WWH ::

Custom Search