Hardware Reference

In-Depth Information

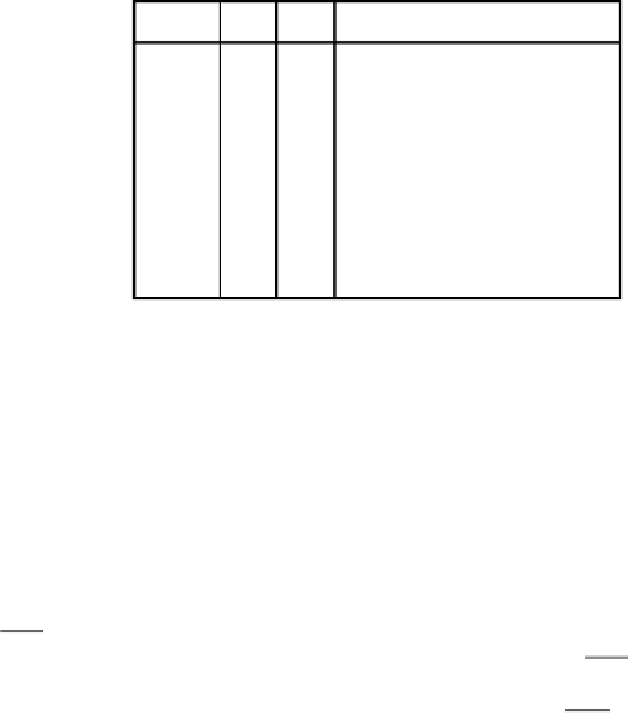

LSTRB

A0

R/W

Type of Access

1

0

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

8-bit read of an even address

8-bit read of an odd address

8-bit write of an even address

8-bit write of an odd address

16-bit read of an even address

16-bit read of an odd address

(low/high bytes swapped)

16-bit write of an even address

16-bit write of an odd address

(low/high bytes swapped)

0

1

0

1

0

0

Table 14.8

■

Access type versus bus control signals

The ECLK signal is provided as a timing reference for external memory accesses. This sig-

nal is controlled by 3 bits.

•

The NECLK bit of the PEAR register

•

The IVIS bit of the MODE register

•

The ESTR bit of the EBICTL register

The NECLK bit enables/disables the E-clock signal. The IVIS bit allows the E-clock to be

visible when the MCU is performing an internal access cycle. The ESTR bit allows the E-clock

to be stretched.

The ECS signal is used as the chip-select signal for external memory chips. Because it is

asserted immediately after the address signals become valid, the ECS signal is often used to

latch address signals so that they can remain valid throughout a complete bus cycle. The rising

edge of the E-clock can also be used to latch address signals. The XCS signal, available in some

HCS12 devices only, is also used as the external chip-select signal for external chips. It can also

be used to latch address signals because of its timing.

The waveform of a typical digital signal is shown in Figure 14.25. A bus signal cannot rise

from low to high or drop from high to low instantaneously. The time needed for a signal to rise

from 10 to 90 percent of the power supply voltage is referred to as the

rise time

(

t

R

). The time

needed for a signal to drop from 90 to 10 percent of the power supply voltage is referred to as the

fall time

(

t

F

).

0.9

V

DD

0.9

V

DD

0.1

V

DD

0.1

V

DD

t

R

t

F

Figure 14.25

■

A typical digital waveform

A single bus signal is often represented as a set of line segments (see Figure 14.26). The

horizontal axis and vertical axis represent the time and the magnitude (in volts), respectively,

of the signal. Multiple signals of the same nature, such as address and data, are often grouped

Search WWH ::

Custom Search