Hardware Reference

In-Depth Information

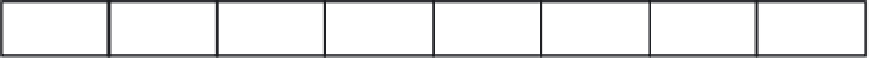

The following registers control the operation of the EEPROM block:

EEPROM C

LOCK

D

IVIDER

R

EGISTER

(ECLKDIV)

The contents of this register are shown in Figure 14.19. The EDIVLD bit is read-only. This

register controls the timing of the EEPROM programming and erasure operation. The contents

of this register are identical to those of the FCLKDIV register. Bits 0,6 can be written once

after reset. The method for selecting an appropriate dividing value for the EEPROM is the same

as that for the flash memory.

7

6

5

4

3

2

1

0

EDIVLD

PRDIV8

EDIV5

EDIV4

EDIV3

EDIV2

EDIV1

EDIV0

base+$100

Reset:

0

0

0

0

0

0

0

0

EDIVLD: clock divider loaded

0 = register has not been written.

1 = register has been written to since the last reset.

PRDIV8: enable prescaler by 8

0 = the input oscillator clock is directly fed into the FCLKDIV divider.

1 = enables a divide-by-8 prescaler, to divide the flash module input oscillator

clock before feeding into the CLKDIV divider.

EDIV[5:0]: clock divider bits

The combination of PRDIV8 and FDIV[5:0] effectively divides the flash module

input oscillator clock down to a frequency of 150 kHz

,

200 kHz. The maximum

divide ratio is 512.

Figure 14.19

■

EEPROM clock divider register (ECLKDIV)

EEPROM C

ONFIGURATION

R

EGISTER

(ECNFG)

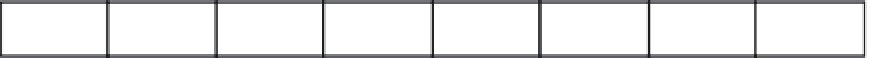

This register enables the EEPROM interrupts. The contents of this register are shown in

Figure 14.20. This register is readable and writable any time.

7

6

5

4

3

2

1

0

CBEIE

base+$113

CCIE

0

0

0

0

0

0

Reset:

0

0

0

0

0

0

0

0

CBEIE: command buffer empty interrupt enable

0 = command buffer empty interrupts disabled.

1 = an interrupt will be requested whenever the CBEIF flag is set.

CCIE: command completion interrupt enable

0 = command complete interrupts disabled.

1 = an interrupt will be requested whenever the CCIF flag is set.

Figure 14.20

■

EEPROM configuration register (ECNFG)

EEPROM P

ROTECTION

R

EGISTER

(EPROT)

This register defines which EEPROM sectors are protected against programming or erasure.

The contents of this register are shown in Figure 14.21. This register is loaded from EEPROM

array at $_FFD in the reset sequence as indicated by the F letter. All bits are readable; bits NV[6:4]

Search WWH ::

Custom Search