Hardware Reference

In-Depth Information

Example 14.1

▼

Write an instruction sequence to remap the register block to $4000.

Solution:

The upper 5 bits of the INITRG register should be 01000. The following instruction

sequence will achieve the desired assignment:

movb

#$40,INITRG

nop

; wait for the remap to take effect

▲

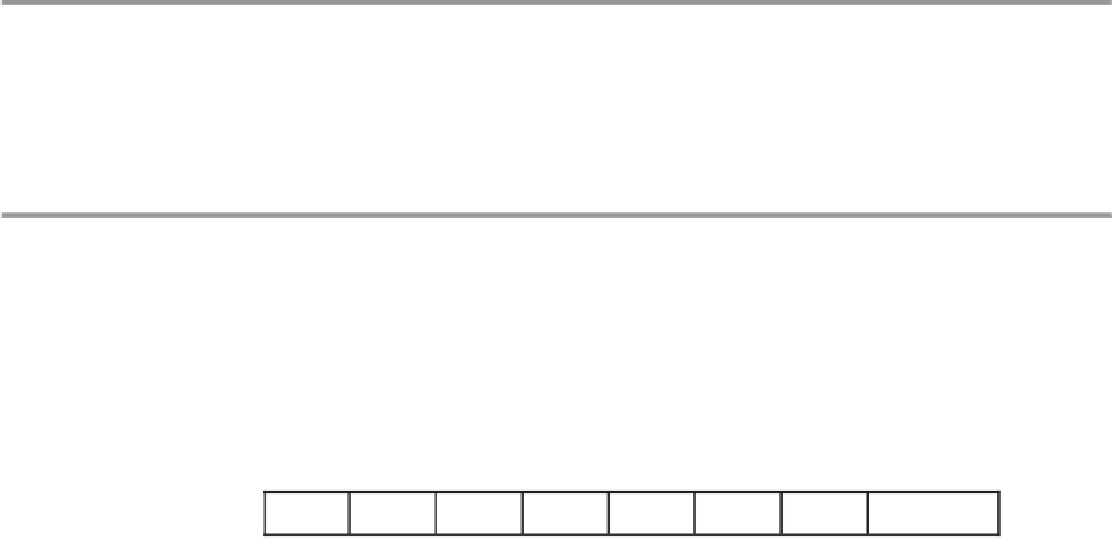

SRAM can be remapped to any 2-kB boundary within the 64-kB memory space. The remap-

ping is controlled by the INITRM register. The contents of the INITRM are shown in Figure

14.2. Bits RAM15 to RAM11 determine the upper 5 bits of the base address for the system's

internal SRAM array. The INITRM register can be written into once in normal modes but many

times in special modes.

7

6

5

4

3

2

1

0

RAM 15

RAM 14

RAM 13

RAM 12

RAM 11

0

0

RAMHAL

base+$10

Value after

reset:

0

0

0

0

1

0

0

0

RAM15

,

RAM11: internal RAM map position

These bits determine the upper 5 bits of the base address for

the system's internal RAM array.

RAMHAL: RAM high-align

0 = aligns the RAM to the lowest address ($0000) of the

mappable space.

1 = aligns the RAM to the highest address ($FFFF) of the

mapping space.

Figure 14.2

■

RAM initialization register (INITRM)

The EEPROM block can be remapped to any 2-kB boundary. The remapping of EEPROM is

controlled by the INITEE register. The contents of this register are shown in Figure 14.3. The

EEPROM is activated by bit 0 of this register. Bits EE15 to EE11 determine the upper 5 bits of

the base address for the system's internal EEPROM array. The INITEE register can be written

any time.

A few registers are involved in the mapping control of more than one memory module. The

functions of these registers are described in this section.

M

ISCELLANEOUS

S

YSTEM

C

ONTROL

R

EGISTER

(MISC)

This register enables/disables the on-chip ROM (including flash memory and EEPROM)

and allows us to stretch the length of the external bus cycle. The contents of this register are

shown in Figure 14.4. The value of the ROMONE pin is latched to the ROMON bit of the

MISC register on the rising edge of the RESET signal. If the ROMONE signal is high when it is

Search WWH ::

Custom Search