Hardware Reference

In-Depth Information

Example 12.4

▼

Assuming that S8C,S1C (ATD0CTL3) are set to 0101 and CC,CA (ATD0CTL5) are set to

110, what is the conversion sequence for this setting?

Solution:

The first channel to be converted is AN6 and there are five channels to be converted.

The conversion sequence is as follows:

AN6, AN7, AN0, AN1, and AN2

▲

All eight 16-bit result registers are organized into a circular ring. The conversion

counter value in the ATD

x

STAT0 register specifies the result register to hold the current

conversion result. In the FIFO mode, the conversion count is not reset to 0 when a new

conversion sequence is started. Since one can set the length of a conversion sequence to a

value between 1 and 8, the first conversion result in a sequence may not be stored in the

ATD

x

DR0 register.

Example 12.5

▼

Assume that the following setting was programmed before a new conversion is started:

•

The conversion counter value in the ATD0STAT0 register is 5.

•

The channel select code of the ATD0CTL5 register is 6.

•

The conversion sequence limit of the ATD0CTL3 register is set to 5.

•

The MULT bit of the ATD0CTL5 register is set to 1.

How would the conversion results be stored when the FIFO mode is selected or not

selected?

Solution:

The conversion counter specifies the result register to hold the first conversion re-

sult. The channel-select code specifies the first analog input channel to be converted, and the

conversion sequence limit specifies the number of channels to be converted. The conversion

results will be stored as shown in Table 12.9.

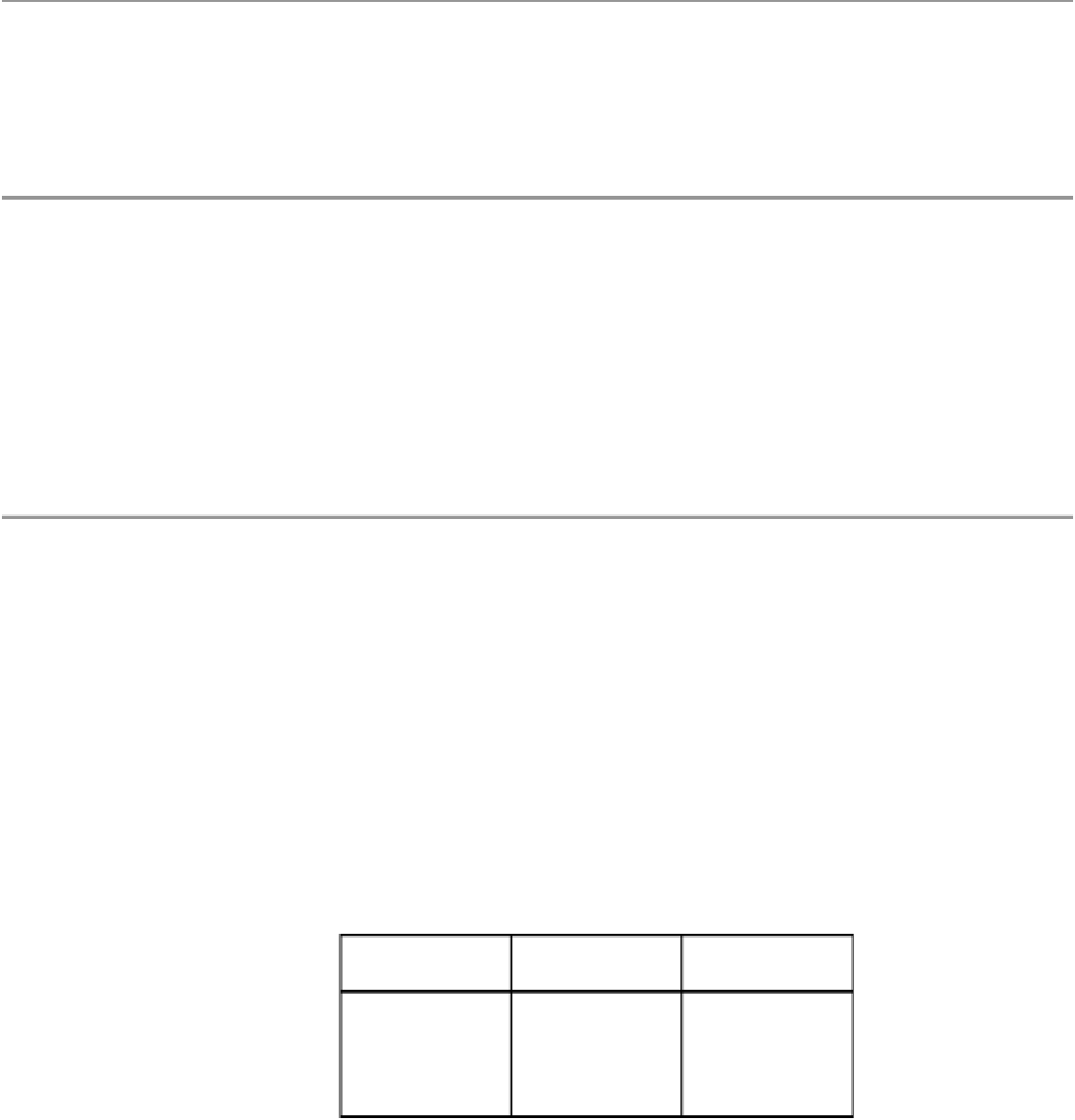

Result Stored in

(FIFO mode)

Result Stored in

(non-FIFO mode)

Analog Channel

AN6

AN7

AN0

AN1

AN2

ATD0DR5

ATD0DR6

ATD0DR7

ATD0DR0

ATD0DR1

ATD0DR0

ATD0DR1

ATD0DR2

ATD0DR3

ATD0DR4

Table 12.9

■

Conversion results storage

▲

Search WWH ::

Custom Search