Hardware Reference

In-Depth Information

The ATD module needs clock signals to perform the conversion. A clock prescaler allows the

ATD module's internal clock to be configured to within the specified frequency range (500 kHz to

2 MHz) for different MCU bus clock frequencies. For maximum accuracy, selecting the 500-kHz

clock is recommended where conversion and sample times are not critical. The bus clock is divided

by a programmable prescaler value (2, 4, 6, . . . , 64) to generate the ATD clock.

As shown in Figure 12.8, a sample-and-hold stage accepts analog signals from the input

multiplexer and stores them as a charge on the sample capacitor. The sampling process has two

stages:

1. Initially, a sample amplifier (of unity gain) is used to buffer the input analog signal for

two cycles to charge the sample capacitor almost to the input potential. This stage

reduces charging and discharging the sample capacitor by the signal source.

2. The sample buffer is then disconnected and the input signal is directly connected to

the storage node for programmable 2, 4, 8, or 16 cycles.

The conversion time of a sample is given by the following equation:

(no. of bits in resolution + no. of programmed sample clocks + 2)

Conversion time =

ATD clock frequency

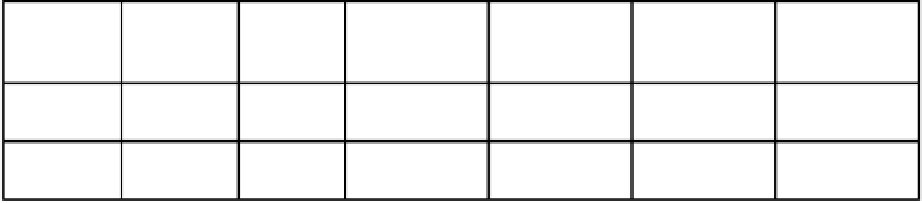

Conversion times for frequencies at 500 kHz and 2 MHz are shown in Table 12.8. For maxi-

mum accuracy, selecting 16 programmable sample cycles is recommended whenever the sam-

ple time is not critical. For fast-changing signals, sample time and source impedance should be

kept low. The actual conversion time is the sum of the converter time and the sample time in

one of the rightmost four columns.

ATD Clock

Frequency

Converter

Time

2 + 2 Sample

Clocks

2 + 4 Sample

Clocks

2 + 8 Sample

Clocks

2 + 16 Sample

Clocks

Resolution

2 MHz

2 MHz

8-bit

1

10-bit

2

4 µs

5 µs

2 µs

3 µs

5 µs

9 µs

500 kHz

500 kHz

8-bit

10-bit

16 µs

20 µs

8 µs

12 µs

20 µs

36 µs

1

The fastest 8-bit resolution conversion time is 4 µs

1

2 µs

5

6 µs.

2

The fastest 10-bit resolution conversion time is 5 µs

1

2 µs

5

7 µs.

Table 12.8

■

ATD conversion timings

In the case of a multiple-channel conversion sequence (MULT bit of the ATD

x

CTL5 regis-

ter 5 1), when the input selector goes past channel AN7, it wraps around to the channel AN0.

Search WWH ::

Custom Search