Hardware Reference

In-Depth Information

way as in a byte write operation. But instead of asserting a stop condition, the master transmits

up to 16 data bytes to the 24LC08B that are temporarily stored in the on-chip page buffer. These

16 data bytes will be written into the memory after the master has asserted a stop condition.

After the receipt of each byte, the 4 lower address pointer bits are internally incremented by 1.

The highest 6 bits of the byte address remain constant. Should the master transmit more than

16 bytes prior to generating the stop condition, the address counter will roll over and the previ-

ously received data will be overwritten.

When the 24LC08B is writing the data held in the write buffer into the EEPROM array, it

will not acknowledge any further write operation. This fact can be used to determine when

the cycle is completed. Once the stop condition for a write command has been issued from

the master, the device initiates the internal write cycle. The ACK polling can be initiated im-

mediately. This involve

s t

he master's sending a start condition followed by the control byte

for a write command (R/W 5 0). If the 24LC08B is still busy, then no ACK will be returned. If

the cycle is complete, then the device will return the ACK, and the master can then proceed

with the next read or write command. The polling process is illustrated in Figure 11.39.

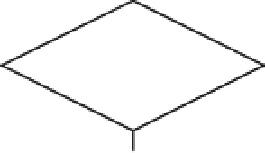

Send

write command

Send stop

condition to

initiate write cycle

Send start

Send con

tro

l byte

with R/W = 0

No

Did device

acknowledge?

Ye s

Next

operation

Figure 11.39

■

Acknowledge polling flow

Search WWH ::

Custom Search