Hardware Reference

In-Depth Information

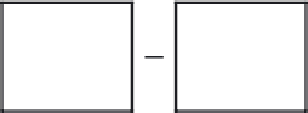

WP

HV generation

Memory

control

logic

EEPROM

array

I/O

control

logic

XDEC

Page latches

YDEC

I/O

SCL

V

cc

S

ens

e amp

R/W control

V

ss

SDA

Figure 11.37

■

Block diagram of 24LC08B

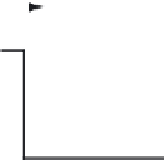

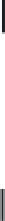

7

6

5

4

3

2

1

0

1

0

1

0

X

B1

B0

R/W

Figure 11.38

■

24LC08B control byte contents

The upper 4 bits are the device ID of the 24LC08B, and the value represented by bits

B1,B0 is the block address of the memory location to be accessed. For any access to the

24LC08B, the master must also send an 8-bit byte address after the control byte. There is an

address pointer inside the 24LC08B. After the access of each byte, the address pointer is incre-

mented by 1.

The 24LC08B supports byte write and pagewrite operations. In a

byte write

operation, the

following operations need to be performed:

1. The master asserts the start condition and sends the control byte to the 24LC08B.

2. The 24LC08B acknowledges the data transmission.

3. The master sends the byte address to the 24LC08B.

4. The 24LC08B acknowledges the data transmission.

5. The master sends the data byte to the 24LC08B.

6. The 24LC08B acknowledges the data transmission.

7. The master asserts the stop condition.

In a

pagewrite

operation, the master can send up to 16 bytes of data to the 24LC08B. The write

control byte, byte address, and the fi rst data byte are transmitted to the 24LC08B in the same

Search WWH ::

Custom Search