Hardware Reference

In-Depth Information

this programmable part at the reception of this 2-byte sequence. The device will

not reset.

•

00000000 (0x00). This code is not allowed to be used as the second byte.

Sequences of programming procedure are published in the appropriate device data sheets. The

remaining codes have not been fi xed, and devices must ignore them.

When bit B is 1, the 2-byte sequence is a

hardware general call.

This means that the sequence

is transmitted by a hardware master device, such as a keyboard scanner, which cannot be pro-

grammed to transmit a desired slave address. Since a hardware master does not know in advance

to which device the message has to be transferred, it can only generate this hardware general call

and present its own address to identify itself to the system. The 7 bits remaining in the second

byte contain the address of the hardware master. This address is recognized by an intelligent de-

vice (e.g., a microcontroller) connected to the bus, which will then direct the information from

the hardware master. If the hardware master can also act as a slave, the slave address is identical

to the master address. In some systems, an alternative could be that the hardware master trans-

mitter is set in the slave receiver mode after the system reset. In this way, a system-configuring

master can tell the hardware master transmitter (which is now in slave receiver mode) to which

address data must be sent (see Figure 11.15). After this programming procedure, the hardware

master remains in the master transmitter mode.

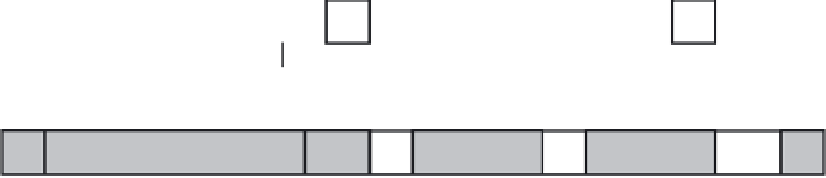

S

A

Dump addr. for H/W master

XA P

Slave addr. H/W master

R/W

Write

(a) Configuring master sends dump address to

hardware master

Dump addr. for H/W master

A

A

Data

A

Data

P

R/W

A/A

Write

(b) Hardware master dumps data to selected slave

Figure 11.15

■

Data transfer by a hardware transmitter capable of dumping data

directly to slave devices

Ten-bit addressing is compatible with, and can be combined with, 7-bit addressing. Using

10-bit addressing exploits the reserved combination 1111xxx for the first 7 bits of the first

byte following a start (S) or repeated start (R) condition. The 10-bit addressing does not affect

the existing 7-bit addressing. Devices with 7-bit and 10-bit addresses can be connected to the

same I

2

C bus, and both 7-bit and 10-bit addressing can be used in standard- and fast-mode sys-

tems. Although there are eight possible combinations of the reserved address bits 1111xxx, only

the four combinations 11110xx are used for 10-bit addressing. The remaining four combina-

tions 11111xx are reserved for future I

2

C bus enhancements.

D

EFINITIONS

OF

B

ITS

IN

THE

F

IRST

2 B

YTES

The 10-bit slave address is formed from the first 2 bytes following a start (S) condition

or repeated start (R) condition. The first 7 bits of the first byte are the combination 11110xx,

of which the last 2 bits (xx) are the 2 most significant bits of the 10-bit address. The eighth bit

Search WWH ::

Custom Search