Hardware Reference

In-Depth Information

S

TOP

(P) C

ONDITION

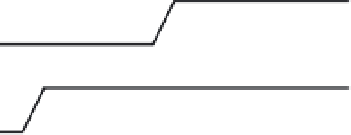

A stop condition indicates that a device wants to release the I

2

C bus. Once released (the

driver is turned off), other devices may use the bus to transmit data. As shown in Figure 11.3, a

stop condition is represented by the SDA signal going high when the clock (SCL) signal is high.

SDA

SCL

Figure 11.3

■

Stop (P) condition

Once the stop condition completes, both the SCL and the SDA signals will be high. This is

considered to be an

idle bus

. After the bus is idle, a start condition can be used to send more data.

R

EPEATED

S

TART

(R) C

ONDITION

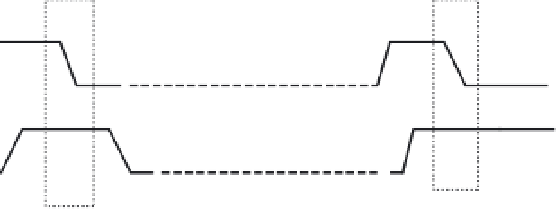

A repeated start signal is a start signal generated without first generating a stop signal to

terminate the communication. This is used by the master to communicate with another slave

or with the same slave in a different mode (transmit/receive mode) without releasing the bus. A

repeated start condition indicates that a device would like to send more data instead of releasing

the line. This is done when a start must be sent but a stop has not occurred. It prevents other de-

vices from grabbing the bus between transfers. The timing diagram of a repeated start condition

is shown in Figure 11.4. The repeated start condition is also called a

restart

condition. In the fig-

ure, there is no stop condition occurring between the start condition and the restart condition.

SDA

SCL

Restart

condition

Data transfer

Start condition

Figure 11.4

■

Restart condition

D

ATA

The data block represents the transfer of 8 bits of information. The data is sent on the SDA

line, whereas clock pulses are carried on the SCL line. The clock can be aligned with the data to

indicate whether each bit is a 1 or a 0.

Data on the SDA line is considered valid only when the SCL signal is high. When SCL is

not high, the data is permitted to change. This is how the timing of each bit works. Data bytes

Search WWH ::

Custom Search